ART ALT

# REGISTER Nº 1998

KAM-143B/TSEC

# **REPAIR AND MAINTENANCE**

# INSTRUCTIONS

FOR

# TSEC/KW-7 (FOUO)

Volume I-Description, Installation and Theory of Operation

Upon receipt, consult List of Effective Pages and varify presence of each page

> DEPARTMENT OF DEFENSE NATIONAL SECURITY AGENCY WASHINGTON 25, D. C.

> > Declassified by NSA 03-30-2009 oursuant to E.O. 12958, as amended, FOIA Case# 47709

April 1963

#### DEPARTMENT OF DEFENSE NATIONAL SECURITY AGENCY WASHINGTON 25, D. C.

March 1963

ł

-:

÷

**!**

Ξì.

#### REPAIR AND MAINTENANCE INSTRUCTIONS FOR TSEC/KW-7 (FOUO)-Volume I—Description, Installation and Theory of Operation

#### LETTER OF PROMULGATION

1. This is a CONFIDENTIAL registered publication and will be handled, stored, and accounted for and destroyed in accordance with current regulations of the appropriate Department, Agency, or other controlling authority pertaining to registered cryptomaterial. Formal authorization for access to CONFIDENTIAL cryptomaterial is required for personnel to have access to this publication.

2. This publication will become effective upon receipt. Authorization for the eventual disposal of this publication will be issued at an appropriate time by the Director, National Security Agency.

3. Amendments to this publication will be promulgated by means of printed or electrically transmitted amendments. Individuals entering such amendments shall so indicate on the "Record of Amendments" page included herein as page 5.

4. This publication is distributed to authorized holders of TSEC/KW-7.

5. THIS PUBLICATION CONTAINS INFORMATION AFFECTING THE NA-TIONAL DEFENSE OF THE UNITED STATES WITHIN THE MEANING OF THE ESPIONAGE LAWS, TITLE 18, U.S.C., SECTIONS 793, 794, AND 798. ITS TRANS-MISSION OR THE REVELATION OF ITS CONTENTS IN ANY MANNER TO AN UNAUTHORIZED PERSON IS PROHIBITED BY LAW.

6. Classified extracts from this publication may be made as necessary. Such extracts will be classified CONFIDENTIAL, marked CRYPTO, and accounted for locally until destroyed by burning. Formal authorization for access to CONFIDENTIAL cryptomaterial is required for personnel to have access to such extracts.

7. This publication may not be carried in aircraft for use therein.

In a. Blake

GORDON A. BLAKE Lieutenant General, USAF Director

> ORIGINAL Reverse (Page 2) Blank

CONFIDENTIAL -

3559654

Ť

KAM-143B/TSEC

۰.

.

ORIGINAL **3** Reverse (Page 4) Blank

-CONFIDENTIAL

#### LIST OF EFFECTIVE PAGES

Note: BLANK pages are not indicated in the "Page Numbers" column when they fall within a group listing of page numbers. However, all BLANK pages in the publication are accounted for by means of the notation "Reverse (Page\_\_\_\_) Blank" printed in the lower right-hand corner of each page immediately preceding the BLANK page.

| Subject Matter          | Effective<br>Pages | Page Numbers<br>(Inclusive)     |

|-------------------------|--------------------|---------------------------------|

| Front Cover             | ORIGINAL           | Unnumbered (Reverse Blank)      |

| Letter of Promulgation  | ORIGINAL           | 1 Reverse (Page 2) Blank        |

| List of Effective Pages | ORIGINAL           | 3 Reverse (Page 4) Blank        |

| Record of Amendments    | ORIGINAL           | 5 Reverse (Page 6) Blank        |

| Record of Page Checks   | ORIGINAL           | 78                              |

| Table of Contents       | ORIGINAL           | 9–14                            |

| List of Illustrations   | ORIGINAL           | 1517                            |

| List of Tables          | ORIGINAL           | 17.                             |

| Figure 1-1              | ORIGINAL           | 18                              |

| CHAPTER 1               | ORIGINAL           | 19-22                           |

| CHAPTER 2               | ORIGINAL           | 23–55 Reverse (Page 56) Blank   |

| CHAPTER 3               | ORIGINAL           | 57–111 Reverse (Page 112) Blank |

| CHAPTER 4               | ORIGINAL           | 113–307 (Reverse Blank)         |

| Back Cover              | ORIGINAL           | Unnumbered (Reverse Blank)      |

#### GENERAL INFORMATION ON RECENT EQUIPMENT CHANGES

Several recent changes were made to the TSEC/KW-7 that were not incorporated into the original printing of the repair and maintenance instructions for the TSEC/KW-7. These changes are listed here for information purposes. They will be incorporated into the appropriate volume of the repair and maintenance instructions in the first amendment thereto.

- 1. A special medium-speed flip-flop has been substituted for medium speed flip-flop 1A7MD21.

- 2. The Loop-Inhibit/Allow switch has been removed and a red strap wire has been added between XA11-D and XA11-N. This will only affect the KW-7 during Two-Wire Loop Adapter (KWL-4) operation. This strap will have to be removed to permit the KWL-4 to be used.

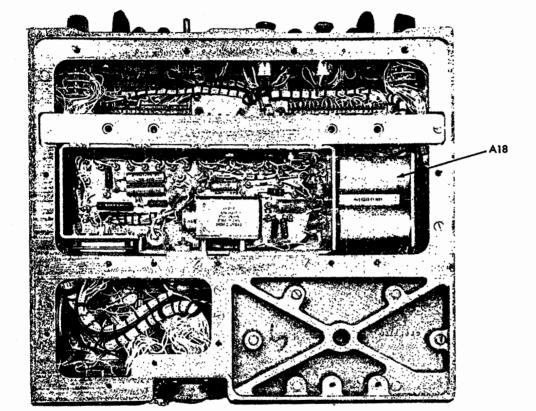

- 3. Some wiring has been changed in the Loop Output Circuit located on Relay Assembly A18. Also a 1 millihenry choke has been added.

- 4. The output of the Time Standard (E-AJY) has been changed from a 7 volt peak-to-peak square wave to a 2 volt rms sine wave.

CONFIDENTIAL-

## CONFIDENTIAL

## KAM-143B/TSEC

| -         | RECORD OF AMENDMENTS                                    |              |                                                                  |  |  |  |  |  |

|-----------|---------------------------------------------------------|--------------|------------------------------------------------------------------|--|--|--|--|--|

|           | Identification of<br>Amendment and<br>Reg. No. (if any) | Date Entered | By Whom Entered<br>(Signature; Renk or<br>Rate; Name of Command) |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

| •         |                                                         |              |                                                                  |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

| •         | · · · · · · · · · · · · · · · · · · ·                   |              |                                                                  |  |  |  |  |  |

|           |                                                         |              | · · · · · · · · · · · · · · · · · · ·                            |  |  |  |  |  |

|           | ·                                                       |              |                                                                  |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

|           |                                                         |              |                                                                  |  |  |  |  |  |

| $\bullet$ |                                                         |              |                                                                  |  |  |  |  |  |

..

•

-CONFIDENTIAL

\_

j,

KAM-143B/TSEC

.

-- CONFIDENTIAL

## **RECORD OF PAGE CHECKS**

.

| Date<br>Checked | By Whom Checked<br>(Signature; Rank or Rate;<br>Name of Command) | Date<br>Checked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | By Whom Checked<br>(Signature; Rank or Rate;<br>Name of Command)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23 angust       |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | and a subscription of the |

| 79ml 70         |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2/ 11/70        |                                                                  | and the second sec | the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 28 Jul 18       |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8 MARSA         |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 01111-00        |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                                                                  | ╁┈──┤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | ······                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | and a second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | ·····                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                                                                  | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |