## **TECHNICAL MANUAL**

# OPERATION AND MAINTENANCE INSTRUCTIONS WITH ILLUSTRATED PARTS BREAKDOWN (ORGANIZATIONAL/INTERMEDIATE)

# RADIO RECEIVER-TRANSMITTER, RT-1446/URC, P/N 10085-0000

(ATOS)

BASIC AND ALL CHANGES HAVE BEEN MERGED TO MAKE THIS A COMPLETE PUBLICATION

<u>DISTRIBUTION STATEMENT</u> - Distribution authorized to US Government agencies only (Administrative or Operational Use) (11 January 1999). Other requests for this document should be referred to WR-ALC/LYE, Robins AFB GA 31098. Questions concerning technical content should be referred to WR-ALC/LYRC.

<u>WARNING</u> - This document contains technical data whose export is restricted by the Arms Export Control Act (Title 22, U.S.C., Sec 2751 et seq.) or the Export Administration Act of 1979, as amended (Title 50, U.S.C., App. 2401 et seq.). Violations of these export laws are subject to severe criminal penalties.

<u>HANDLING AND DESTRUCTION NOTICE</u> - Comply with distribution statement and destroy by any method that will prevent disclosure of the contents or reconstruction of the document.

Published under authority of the Secretary of the Air Force

23 JULY 1985 CHANGE 12 - 12 FEBRUARY 2001

| ST OF EFFEC                     | TIVE PAGE         | s                                                                  |                            |                                                                          |                                     |

|---------------------------------|-------------------|--------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|-------------------------------------|

| 01 01 21120                     |                   | NOTE: The port<br>of the pa                                        |                            | e changes is indicated by a ve<br>are indicated by miniature poin<br>as. |                                     |

| Dates of is                     | ssue for origina  | I and changed pa                                                   | ages are:                  |                                                                          |                                     |

| Change<br>Change<br>Change      |                   |                                                                    | Change<br>Change<br>Change |                                                                          | pril 1995<br>1ary 1999<br>1ary 2000 |

| Change<br>Change<br>Change      | 5<br>6<br>7       | 27 March 1992<br>10 February 1993<br>3 August 1993<br>1 April 1994 | -                          | 12 Febru                                                                 | ary 2001                            |

| TOTAL NUMB                      | 3er of pages in t | HIS PUBLICATION IS                                                 | 368, CONSISTING OF         | THE FOLLOWING:                                                           |                                     |

| Page<br>No.                     | *Change<br>No.    | Page<br>No.                                                        | *Change<br>No.             | Page<br>No.                                                              | *Chang<br>No.                       |

| Title                           | 12                | ß_1                                                                | 2                          | 7-4 - 7-5                                                                |                                     |

| A - B                           |                   |                                                                    | 0                          | 7-4 - 7-3                                                                |                                     |

| C Blank                         |                   |                                                                    |                            | 7-8 - 7-10                                                               |                                     |

| i                               |                   |                                                                    | 0                          | 7-11                                                                     |                                     |

| ii                              |                   |                                                                    |                            | 7-11                                                                     |                                     |

| iii - xv                        |                   |                                                                    | 4                          | 7-12<br>7-13                                                             |                                     |

| 110 - 1-8                       |                   |                                                                    | 4                          | 7-13<br>7-14                                                             |                                     |

|                                 |                   |                                                                    |                            |                                                                          |                                     |

| 1-9                             |                   |                                                                    | 0                          | 7-15                                                                     |                                     |

| 1-10 - 1-12                     |                   |                                                                    | 1                          | 7-16 - 7-19                                                              |                                     |

| 1-13                            |                   |                                                                    | 0                          | 7-20 - 7-21                                                              |                                     |

|                                 | 2                 |                                                                    | 4                          | 7-22                                                                     |                                     |

| 1-14A                           |                   |                                                                    | 0                          | 7-22A                                                                    |                                     |

| 1-14B Blank                     |                   |                                                                    | 5                          | 7-22B Blank                                                              |                                     |

| 1-15 - 1-16                     |                   |                                                                    | 0                          | 8-1                                                                      |                                     |

| 2-1 - 2-7                       |                   |                                                                    | 1                          | 8-2 Blank                                                                |                                     |

| 2-8                             |                   |                                                                    | 0                          | FP-1                                                                     |                                     |

| 2-9 - 2-18                      |                   |                                                                    | 1                          | FP-2 Blank                                                               |                                     |

| 2-19 - 2-20                     |                   |                                                                    | 4                          | FP-3                                                                     |                                     |

| 3-1                             |                   |                                                                    | 0                          | FP-4 Blank                                                               |                                     |

| 3-2                             |                   |                                                                    | 10                         | FP-5                                                                     |                                     |

| 3-2A                            |                   |                                                                    | 0                          | FP-6 Blank                                                               |                                     |

| 3-2B Blank                      | 1                 |                                                                    | 10                         | FP-7                                                                     |                                     |

| 3-3                             |                   |                                                                    | 1                          | FP-8 Blank                                                               |                                     |

| 3-4 - 3-5                       | 0                 | 6-34 - 6-35                                                        | 0                          | FP-9                                                                     |                                     |

| 3-6                             | 3                 | 6-36                                                               | 1                          | FP-10 Blank                                                              |                                     |

| 3-7                             | 0                 | 6-37                                                               | 2                          | FP-11                                                                    |                                     |

| 3-8 Blank                       | 0                 | 6-38                                                               | 0                          | FP-12 Blank                                                              |                                     |

| 4-1 - 4-16                      | 0                 | 6-39 - 6-40                                                        | 11                         | FP-13                                                                    |                                     |

| 4-16A                           |                   | 6-41 - 6-42                                                        | 10                         | FP-14 Blank                                                              |                                     |

| 4-16B Blank                     |                   |                                                                    |                            | FP-15                                                                    |                                     |

| 4-17                            |                   |                                                                    | 0                          | FP-16 Blank                                                              |                                     |

| 4-18 - 4-22                     |                   |                                                                    | 3                          | FP-17                                                                    |                                     |

| 4-23                            |                   |                                                                    | 0                          | FP-18 Blank                                                              |                                     |

| 4-24 - 4-26                     |                   |                                                                    | 3                          | FP-19                                                                    |                                     |

| T &T T &U                       |                   |                                                                    | 0                          | FP-20 Blank                                                              |                                     |

| 5-1 - 5-3                       |                   |                                                                    |                            |                                                                          |                                     |

| 5-1 - 5-3                       |                   |                                                                    | 3                          | FD 91                                                                    |                                     |

| 5-1 - 5-3<br>5-4<br>5-5 - 5-137 | 1                 | 6-55                                                               | 3                          | FP-21<br>FP-22 Blank                                                     |                                     |

$^{\star}\mbox{Zero}$  in this column indicates an original page

A

## LIST OF EFFECTIVE PAGES

| Page<br>No. | *Change<br>No. | Page<br>No. | *Cha<br>No | 0 | Page<br>No. | *Change<br>No. |

|-------------|----------------|-------------|------------|---|-------------|----------------|

|             | 0              |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

| FP-28 Blank | 0              |             |            |   |             |                |

| FP-29       |                |             |            |   |             |                |

| FP-30 Blank | 0              |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

| FP-32 Blank | 0              |             |            |   |             |                |

| FP-33       | 0              |             |            |   |             |                |

| FP-34 Blank | 0              |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

| FP-36 Blank | 0              |             |            |   |             |                |

| FP-37       |                |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

| FP-39       | 0              |             |            |   |             |                |

| FP-40 Blank | 0              |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

| FP-42 Blank | 0              |             |            |   |             |                |

| FP-43       | 0              |             |            |   |             |                |

| FP-44 Blank | 0              |             |            |   |             |                |

| FP-45       |                |             |            |   |             |                |

| FP-46 Blank |                |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

| FP-48 Blank | 0              |             |            |   |             |                |

|             | 0              |             |            |   |             |                |

| FP-50 Blank | 0              |             |            |   |             |                |

#### SAFETY SUMMARY

The following are general safety precautions that are not related to any specific procedures and therefore do not appear elsewhere in this publication. These are recommended precautions that personnel must understand and apply during many phases of operation and maintenance.

#### KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must at all times observe all safety regulations. Do not replace components inside the equipment with the power supply turned on. Under certain conditions, dangerous potentials may exist when the power control is in the off position, due to charges retained by capacitors. To avoid casualties, always remove power and discharge circuits to ground before touching any circuit components. Remove watches and rings before performing any maintenance procedures.

#### DO NOT SERVICE OR ADJUST ALONE

Under no circumstances should any person reach into or enter the enclosure for the purpose of servicing or adjusting the equipment except in the presence of someone who is capable of rendering aid.

#### RESUSCITATION

Personnel working with or near high voltages should be familiar with modern methods of resuscitation. Cardiopulmonary resuscitation procedures are outlined in T.O. 31-1-141-1, and annual refresher training requirements are outlined in AFOSH STD 127-50. The following warnings appear in the text in this volume, and are repeated here for emphasis.

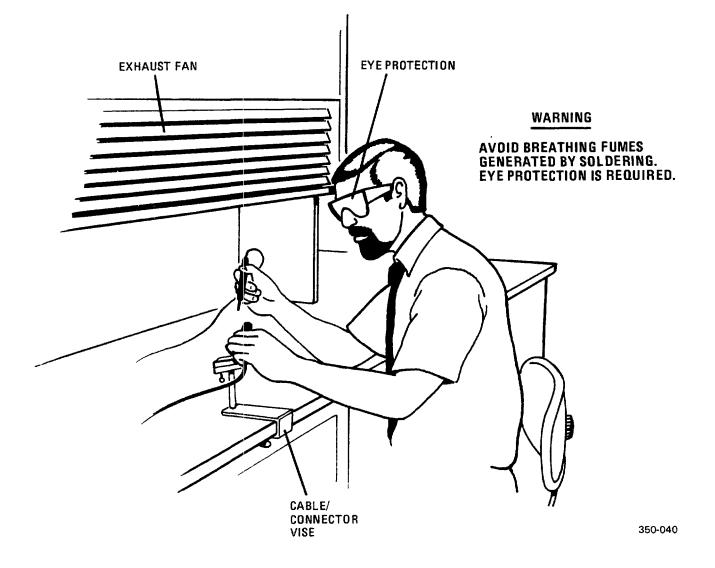

Avoid breathing fumes generated by soldering. Eye protection is required.

Dangerous voltages exist in this radio equipment. Before removing any cover, disconnect primary power.

Do not dispose of lithium batteries in the trash. These batteries contain hazardous materials that can contaminate the environment.

#### HANDLING OF ELECTROSTATIC DISCHARGE SENSITIVE DEVICES (ESDS)

Electrostatic Discharge Sensitive Devices (ESDS) must be handled with certain precautions that must be followed to minimize the effect of static build-up. Consult T.O. 00-25-234, DOD Std-1686, and DOD HDBK 263. ESDS devices are identified in this technical order by the following symbol:

i

#### TABLE OF CONTENTS

#### Section/Para

#### CHAPTER 1. GENERAL INFORMATION

Page

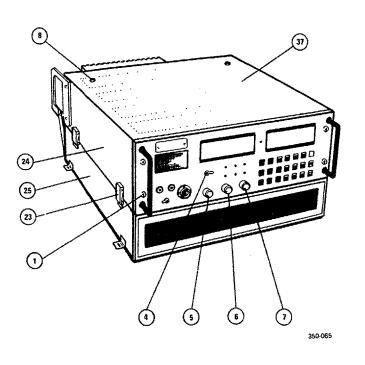

| 1-1.  | General Description and Use         | 1-1 |

|-------|-------------------------------------|-----|

| 1-2.  | Equipment Functional Description    | 1-1 |

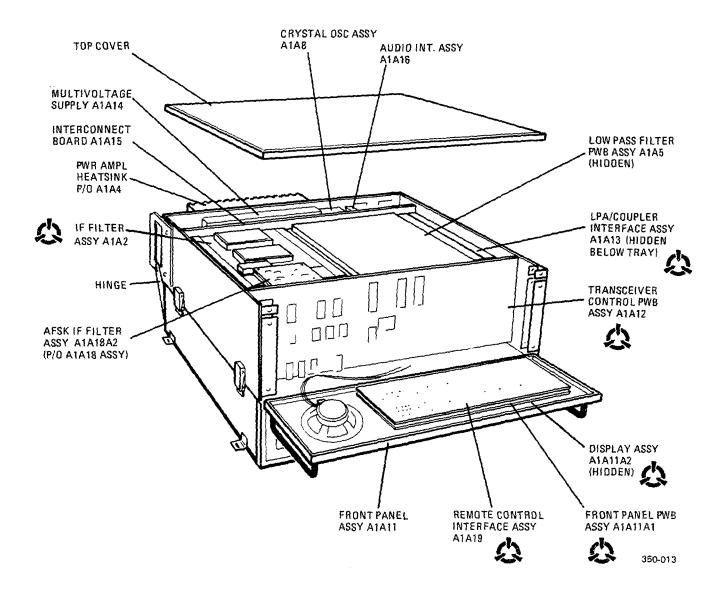

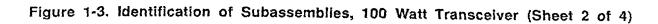

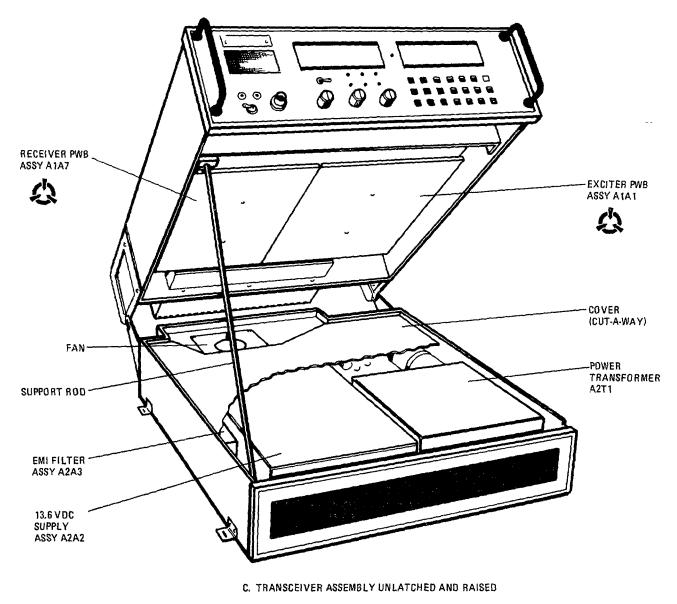

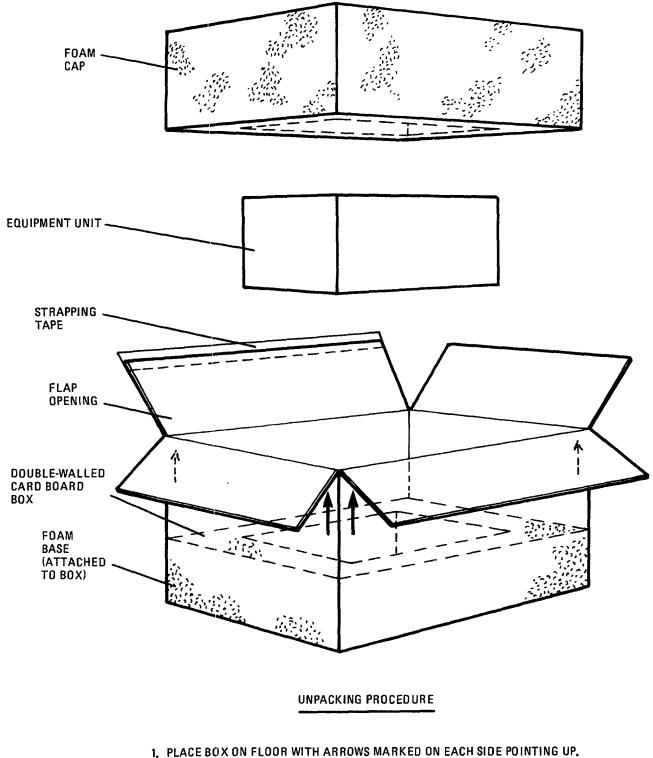

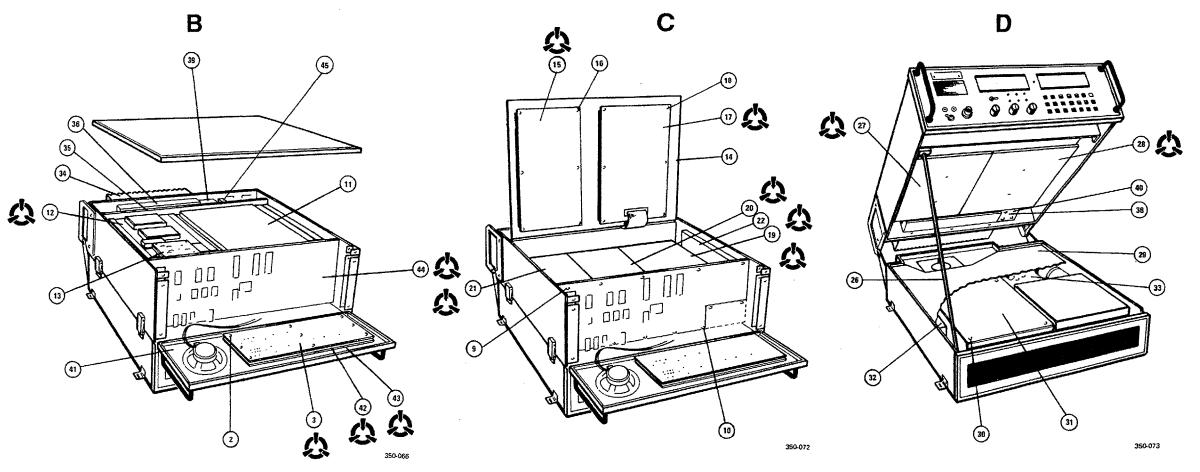

| 1-3.  | Mechanical Design                   | 1-3 |

| 1-4.  | Leading Particulars                 | 1-3 |

| 1-5.  | Capabilities and Limitations        | 1-3 |

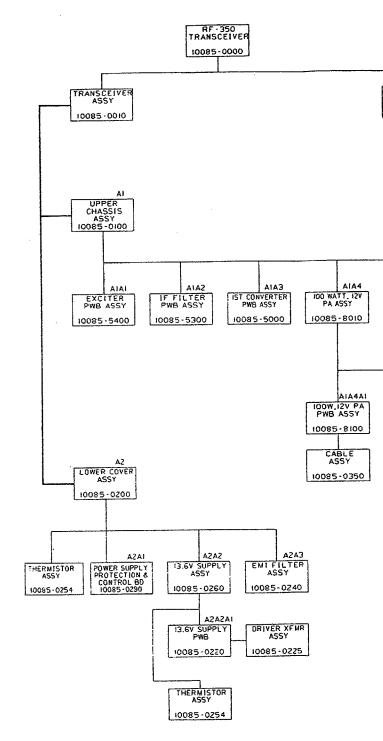

| 1-6.  | Equipment and Accessories Supplied  | 1-3 |

| 1-7.  | Equipment Required But Not Supplied | 1-3 |

| 1-8.  | Special Tools and Test Equipment    | 1-8 |

| 1-9.  | AFSK Option                         | 1-8 |

| 1-10. | Related Publications                | 1-8 |

#### CHAPTER 2. INSTALLATION

#### INSTALLATION LOGISTICS

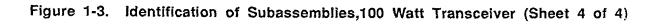

| 2-1. | Equipment Unpacking Procedure | 2-1   |

|------|-------------------------------|-------|

| 2-2. | Preparation for Installation  | 2 - 1 |

#### INSTALLATION PROCEDURE

| 2-3. | Installation Manpower and Manhour Requirements | 2-8  |

|------|------------------------------------------------|------|

| 2-4. | Installation Sequence                          | 2-8  |

|      | Installation Complete Check                    |      |

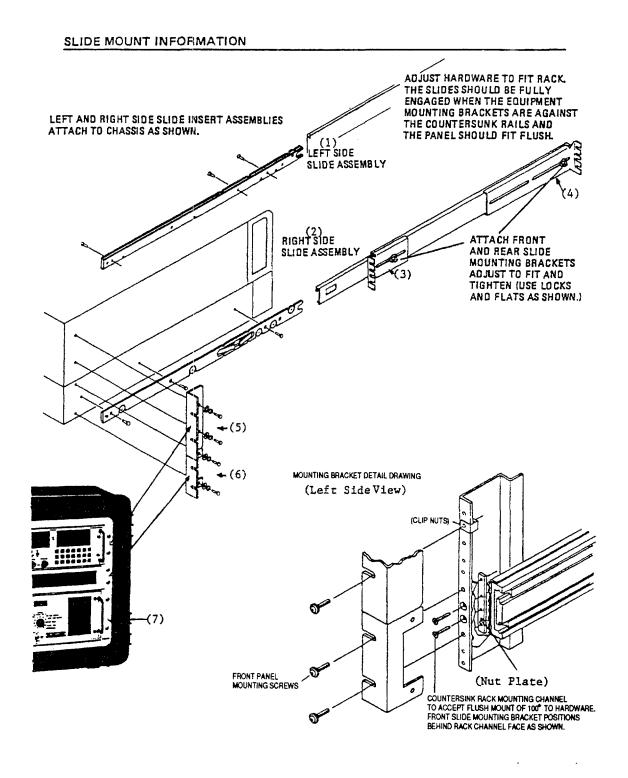

| 2-6. | Slide Mount Information                        | 2-20 |

#### CHAPTER 3. PREPARATION FOR USE AND RESHIPMENT

#### PREPARATION FOR USE

| 3-1. | Initial Control Settings  | 3-1   |

|------|---------------------------|-------|

| 3-2. | Initial Power Application | 3-1   |

| 3-3. | Sequence for Power-Up     | 3-1   |

| 3-4. | Initial Checkout          | 3 - 2 |

#### PREPARATION FOR RESHIPMENT

| 3-5. | Preparation | for | Reshipment |  | 3 - | 7 |

|------|-------------|-----|------------|--|-----|---|

|------|-------------|-----|------------|--|-----|---|

#### CHAPTER 4. OPERATION

#### CONTROLS AND INDICATORS

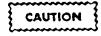

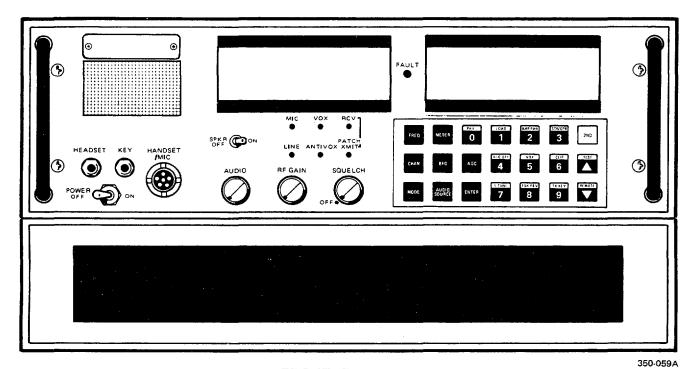

| 4-1. | Control and Indicator Descriptions | 4-1 |

|------|------------------------------------|-----|

| 4-2. | Transceiver Keypad Control         | 4-1 |

| 4-3. | Operating Instructions             | 4-1 |

I

## TABLE OF CONTENTS (Continued)

#### Section/Para

Page

| 11 | OPERAT |

|----|--------|

|    |        |

## OPERATING INSTRUCTIONS

| 4-4.  | Introduction                                 | 4-13 |

|-------|----------------------------------------------|------|

| 4-5.  | Operating Sequences                          | 4-13 |

| 4-6.  | Sequencing of Controls                       | 4-13 |

| 4-7.  | Connection of External Equipment             | 4-13 |

| 4-8.  | External Connections                         | 4-13 |

| 4-9.  | Power Application and Warmup                 | 4-14 |

| 4-10. | Power Application Operator Sequence          | 4-14 |

| 4-11. | Analog Control Positioning                   | 4-14 |

| 4-12. | Control Operation During Periods of Transmit | 4-15 |

| 4-13. | Frequency Selection.                         | 4-15 |

| 4-14. | Channel Selection                            | 4-15 |

| 4-15. | Mode Selection                               | 4-16 |

| 4-16. | Audio Source Selection                       | 4-16 |

| 4-17. | AGC Selection                                | 4-17 |

| 4-18. | VOX Selection.                               | 4-17 |

| 4-19. | BFO Selection                                | 4-17 |

| 4-20. | Clip Selection                               | 4-18 |

| 4-21. | Sidetone Selection                           | 4-18 |

| 4-22. | FSK Rev Selection                            | 4-18 |

| 4-23. | TX Key Selection                             | 4-18 |

| 4-24. | USB and LSB Operation                        | 4-18 |

| 4-25. | AME Operation                                | 4-19 |

| 4-26. | CW Operation                                 | 4-19 |

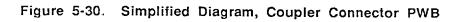

| 4-27. | AFSK Operation                               | 4-20 |

| 4-28. | Remote Operation                             | 4-20 |

| 4-29. | Linear Power Amplifier Operation             | 4-21 |

| 4-30. | Antenna Coupler Operation                    | 4-21 |

| 4-31. | Front Panel Adjustments                      | 4-22 |

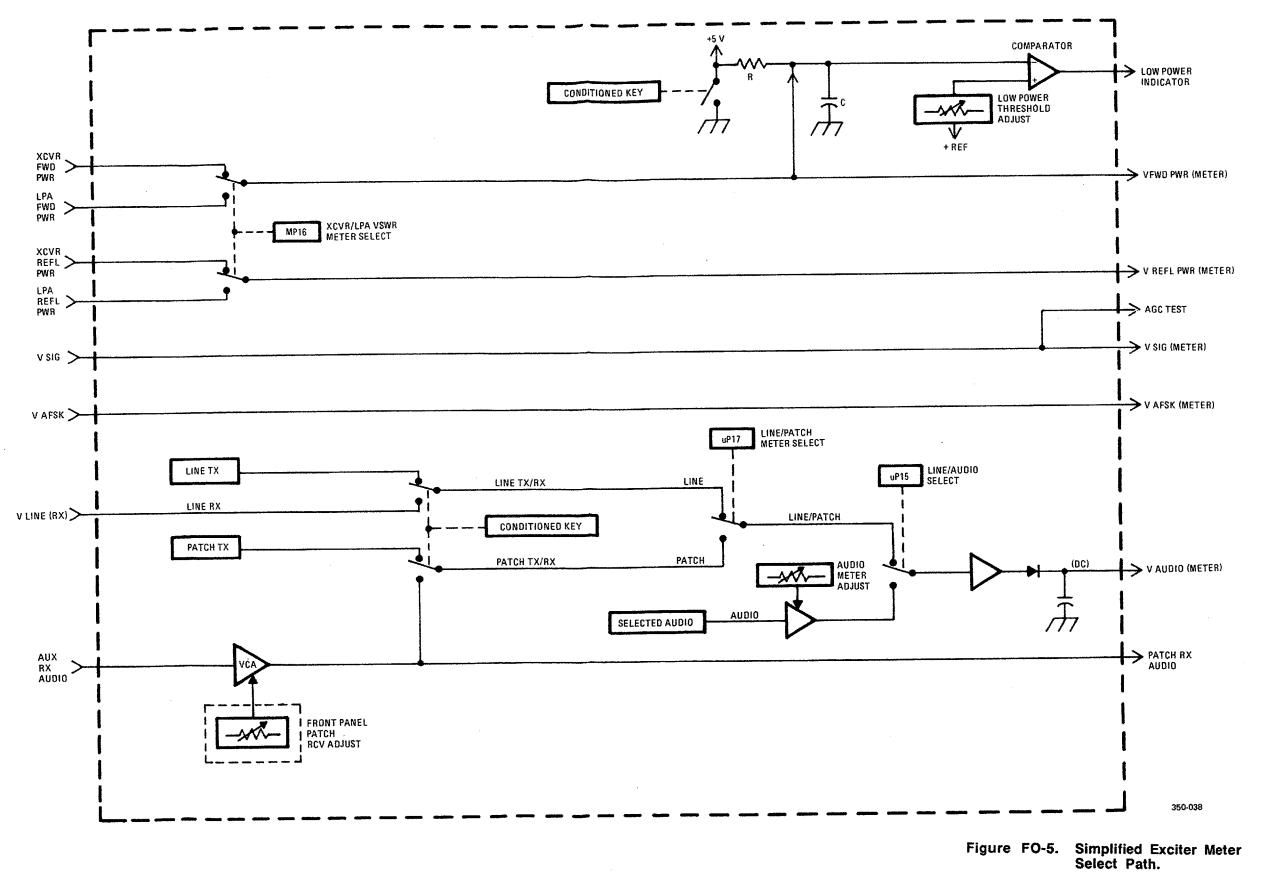

| 4-32. | BIT Fault Interpretation                     | 4-23 |

| 4-33. | Power, VSWR, and Audio Metering              | 4-24 |

| 4-34. | Programming of Preset Channels               | 4-25 |

|       |                                              |      |

#### III EMERGENCY OPERATION

| 4-35. | Conditions for Emergency Operation | 4-26 |

|-------|------------------------------------|------|

|-------|------------------------------------|------|

#### CHAPTER 5. THEORY OF OPERATION

#### I FUNCTIONAL SYSTEM OPERATION

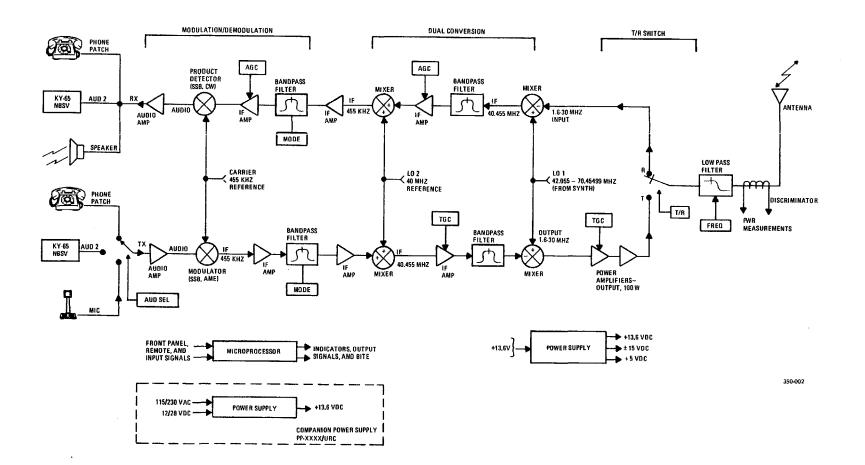

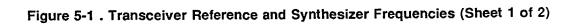

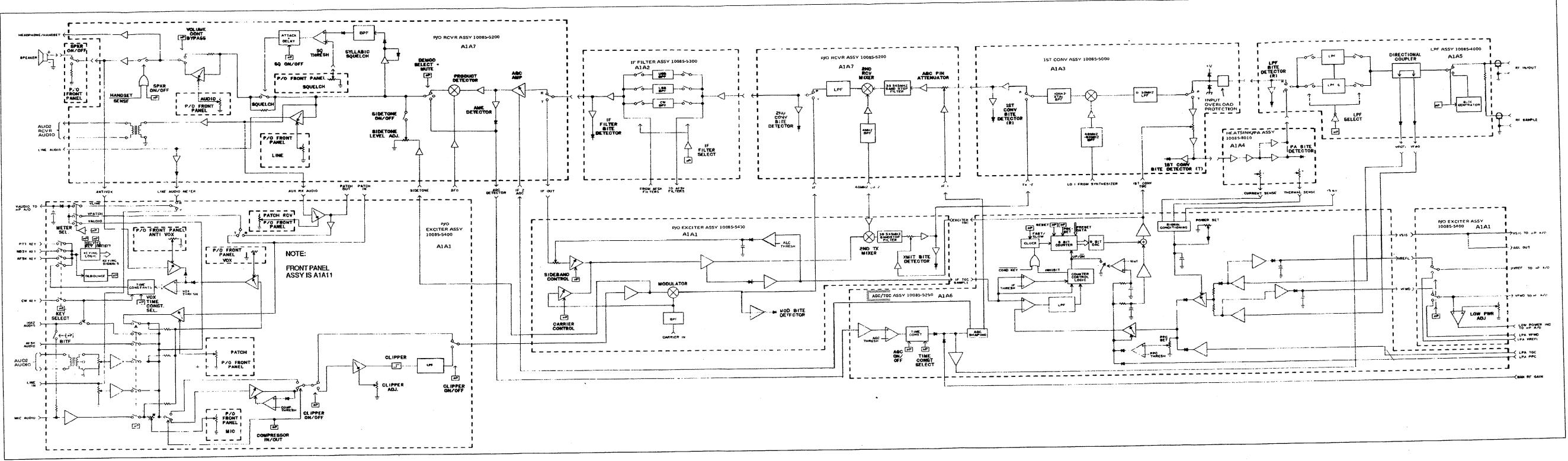

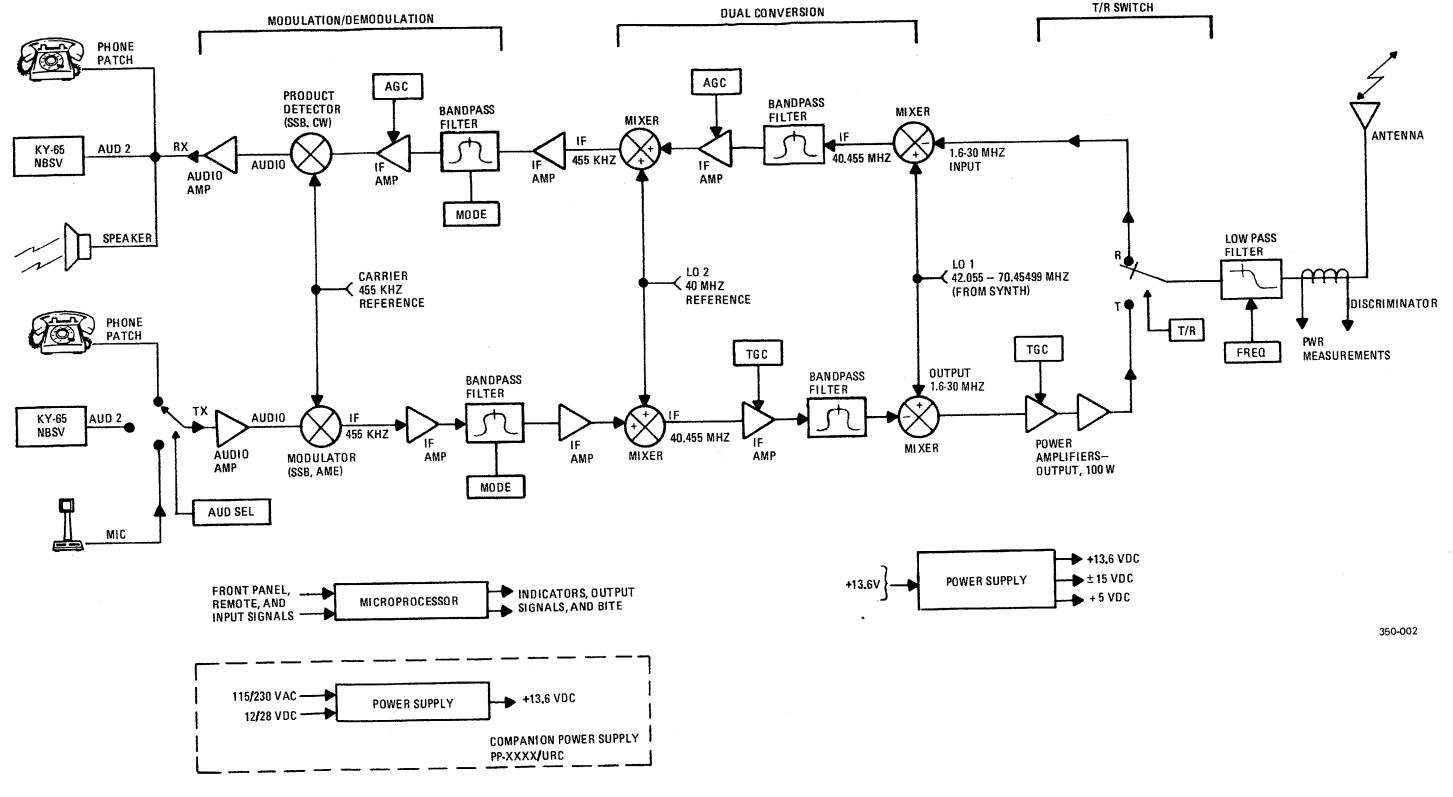

| 5-1. | Transceiver Functional Operation                                           | 5-1 |

|------|----------------------------------------------------------------------------|-----|

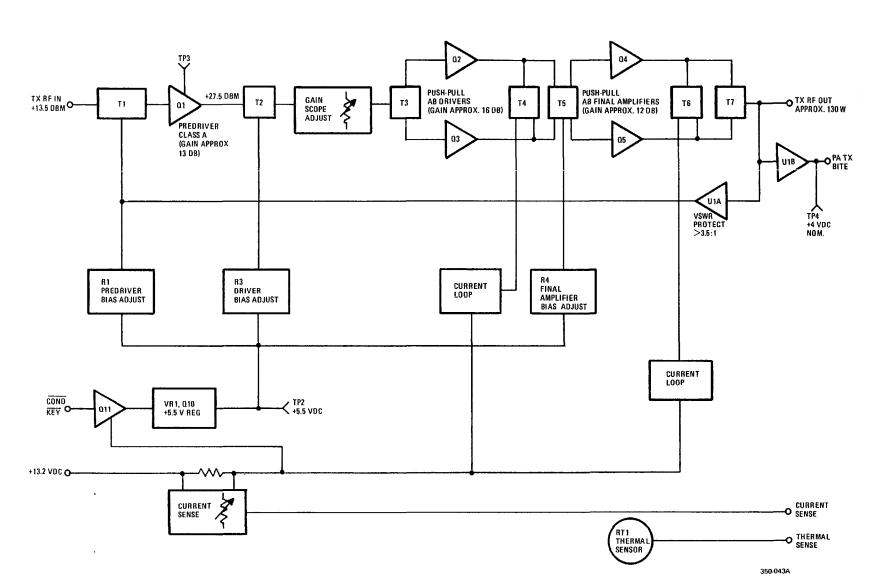

| 5-2. | Transceiver Operating as a Receiver                                        | 5-1 |

| 5-3. | Transceiver Operating as a Transmitter                                     | 5-1 |

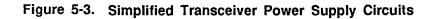

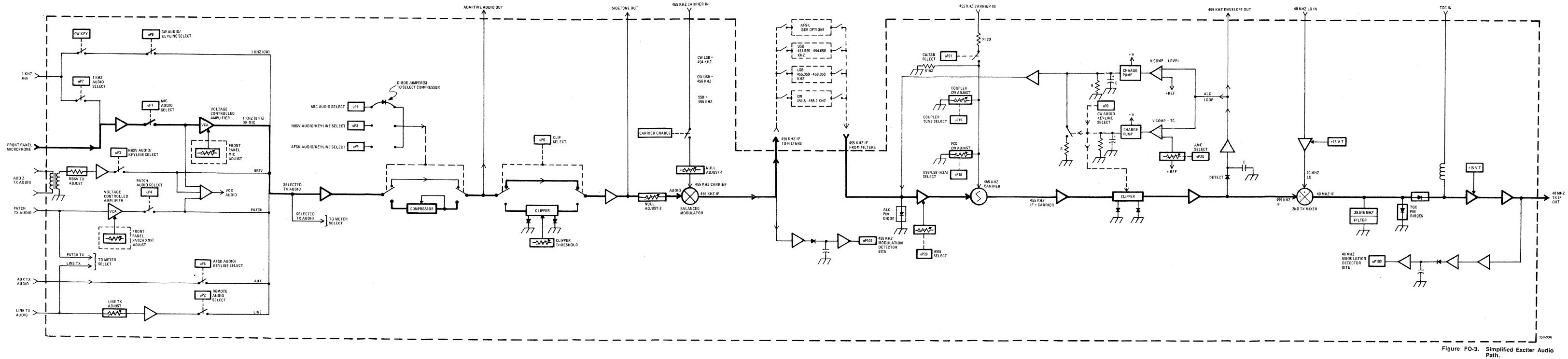

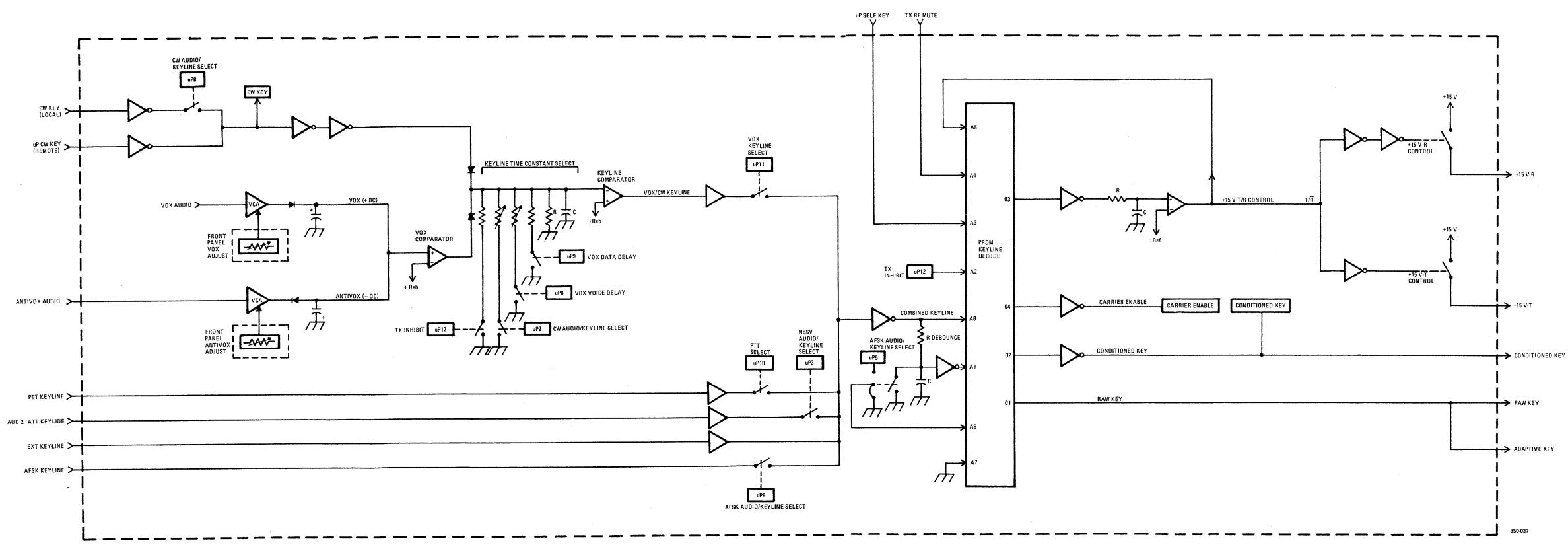

| 5-4. | Functional Operation and Signal Flow of Transmitting Circuits              | 5-1 |

| 5-5. | Functional Operation and Signal Flow of Receiving Circuits                 | 5-5 |

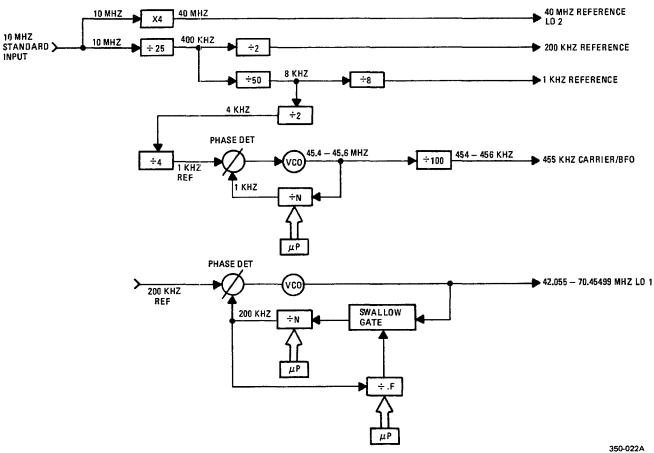

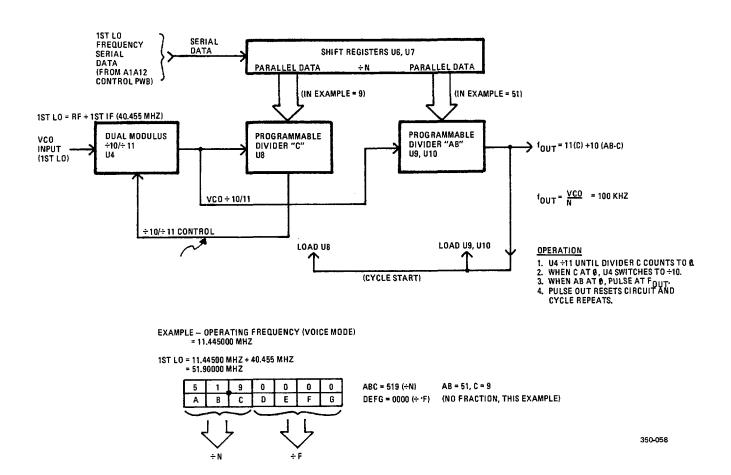

| 5-6. | Functional Operation and Signal Flow of Synthesizer and Reference Circuits | 5-5 |

## T.O. 31R2-2URC-81

#### -TABLE OF CONTENTS (Continued)

## Section/Para

||

## FUNCTIONAL OPERATION OF ELECTRONIC CIRCUITS

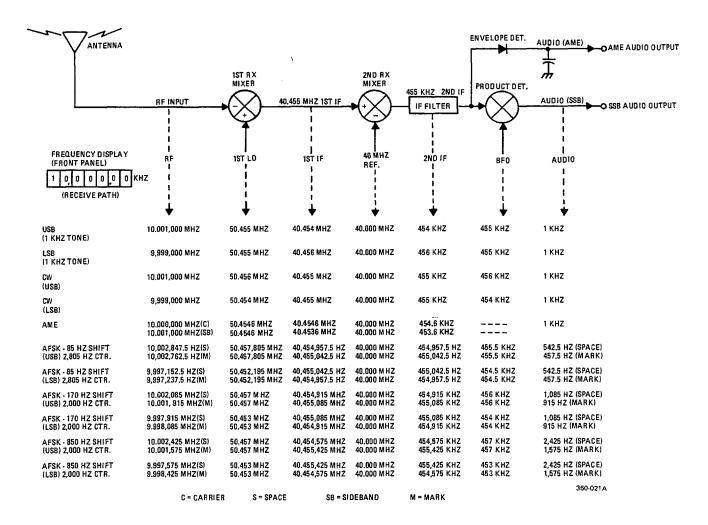

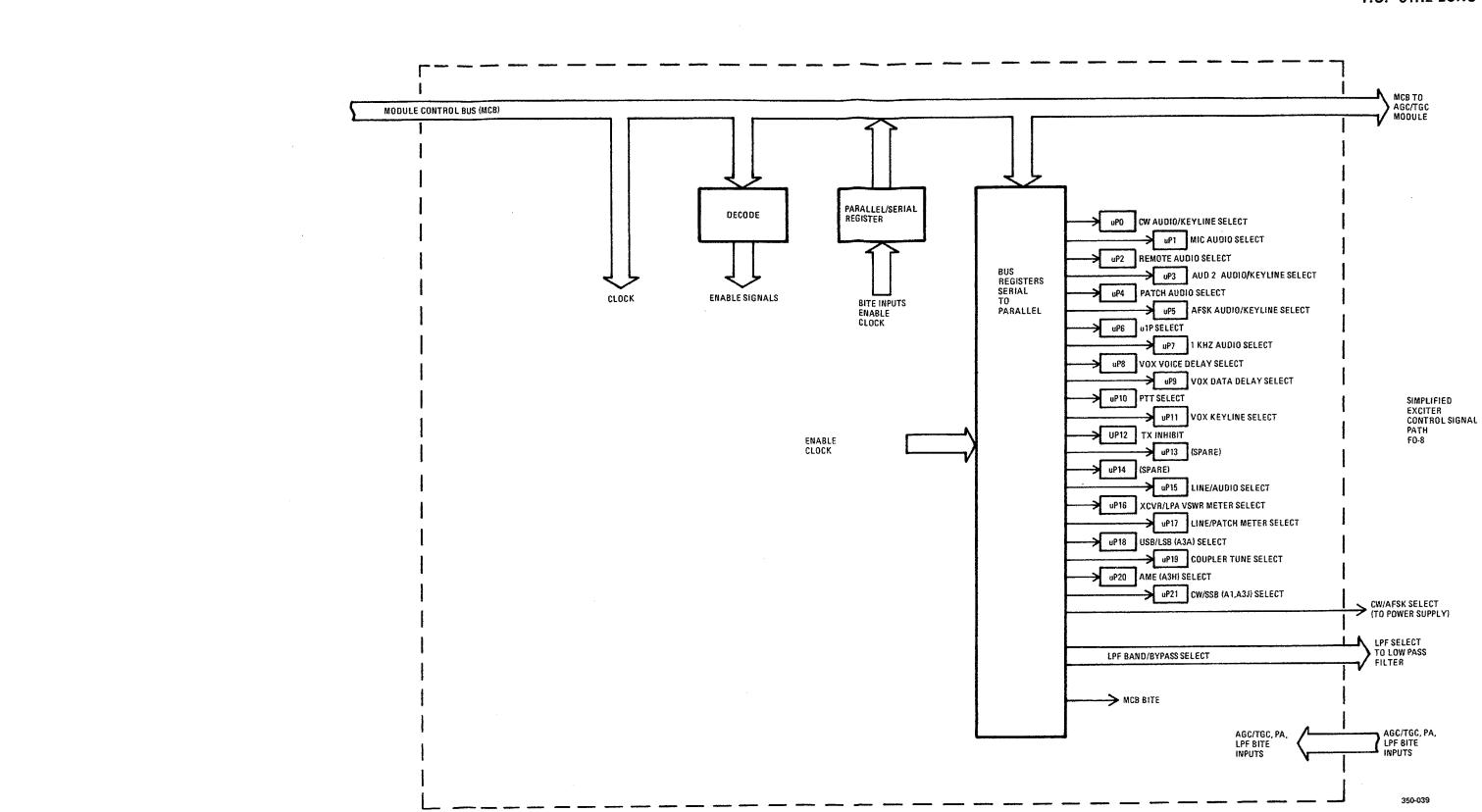

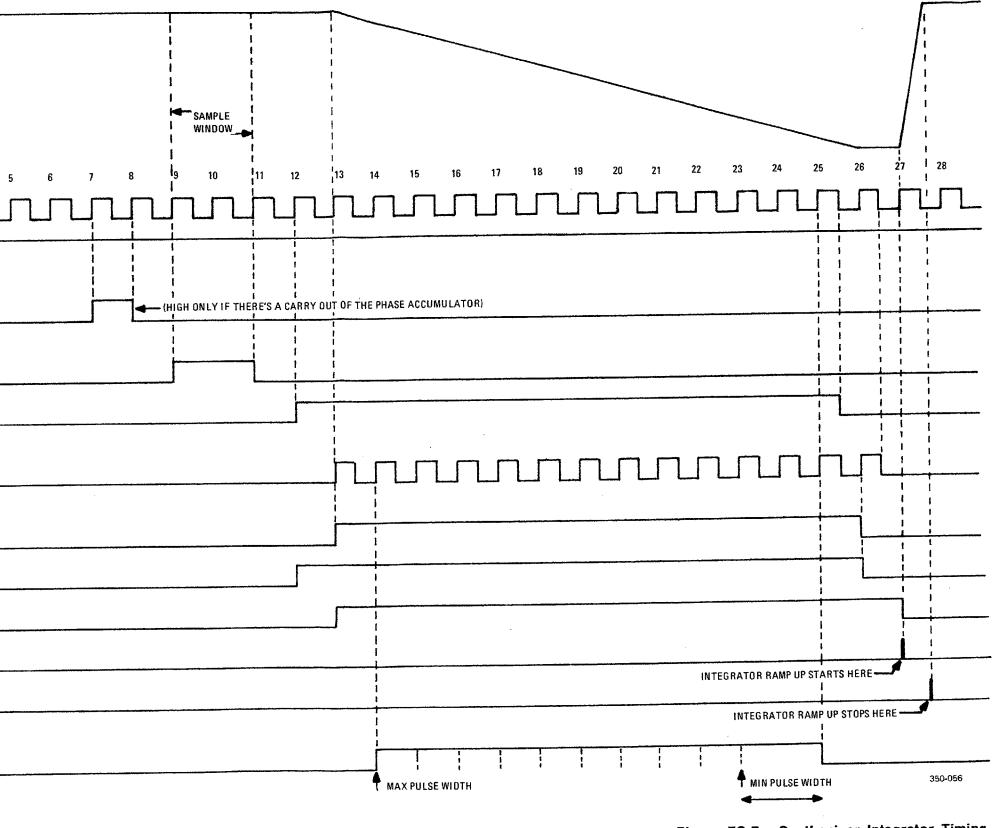

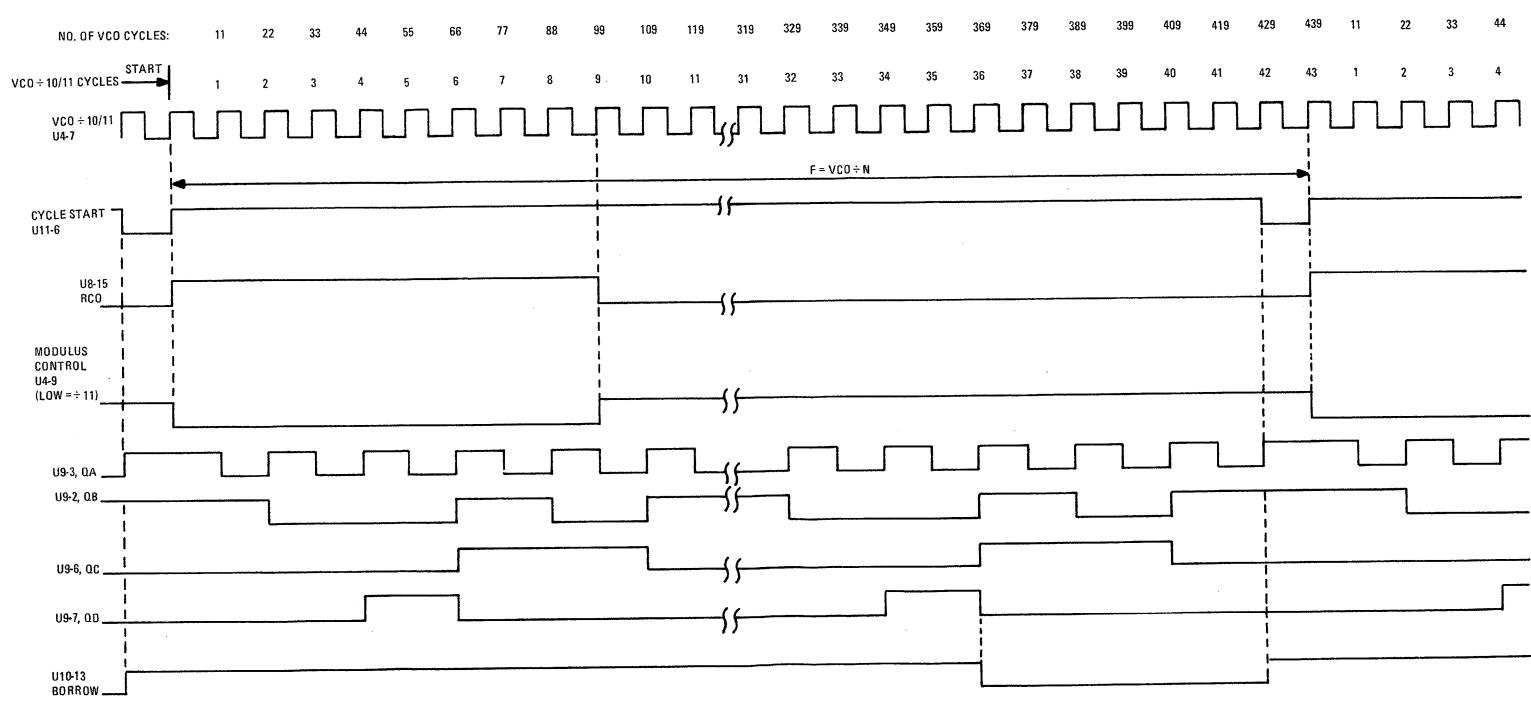

| 5-7.           | Functional Operation and Signal Flow of Transceiver Control Circuits | 7  |

|----------------|----------------------------------------------------------------------|----|

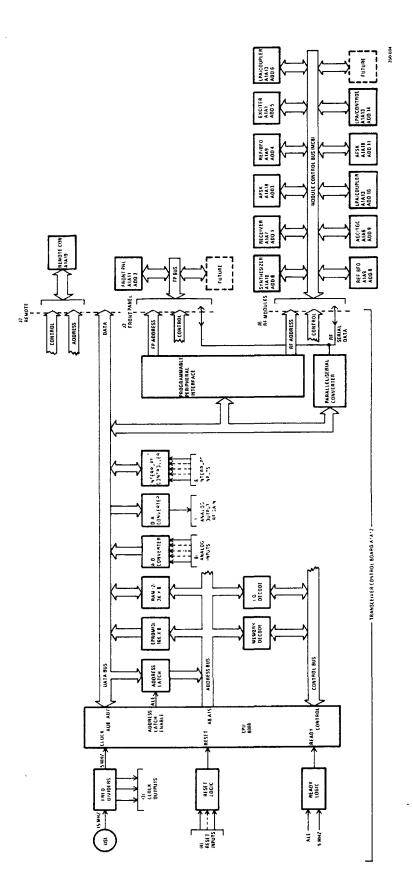

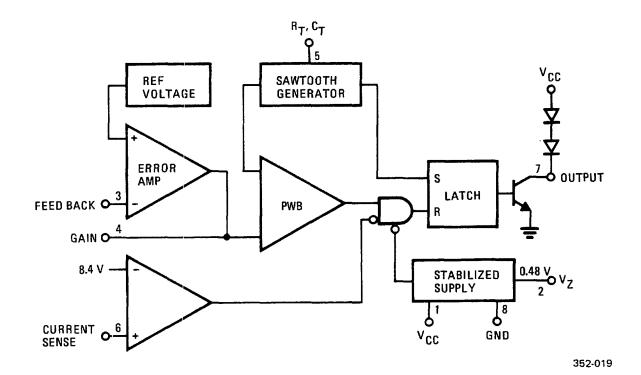

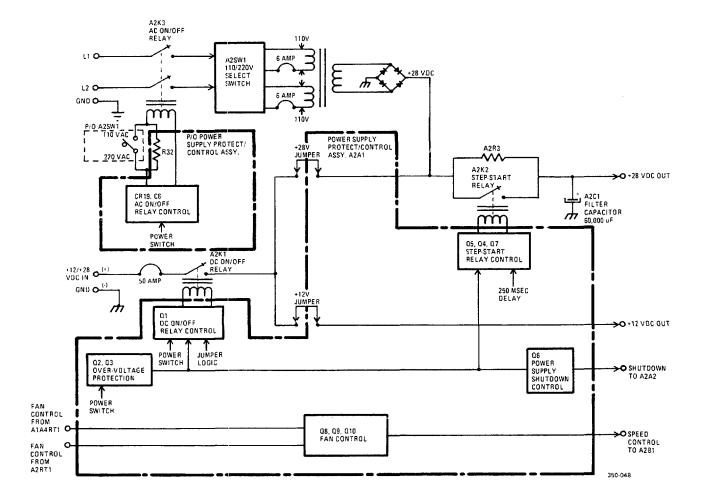

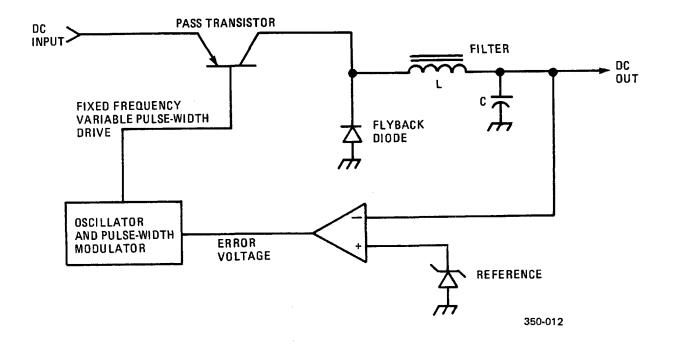

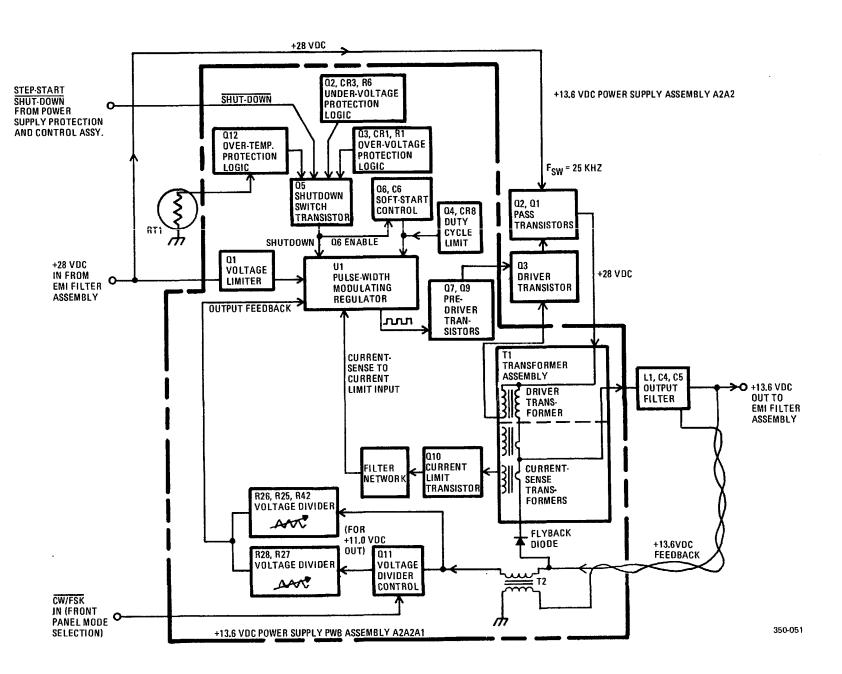

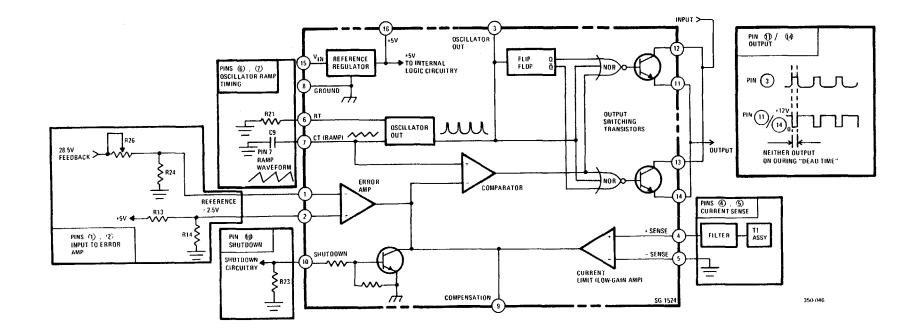

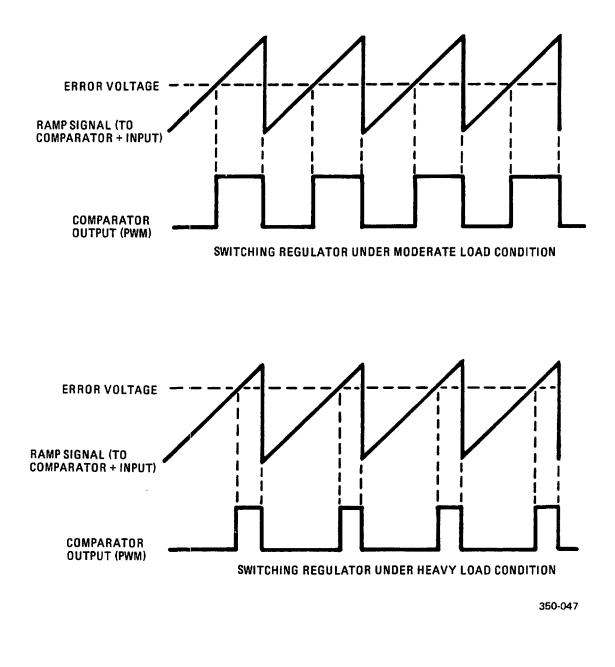

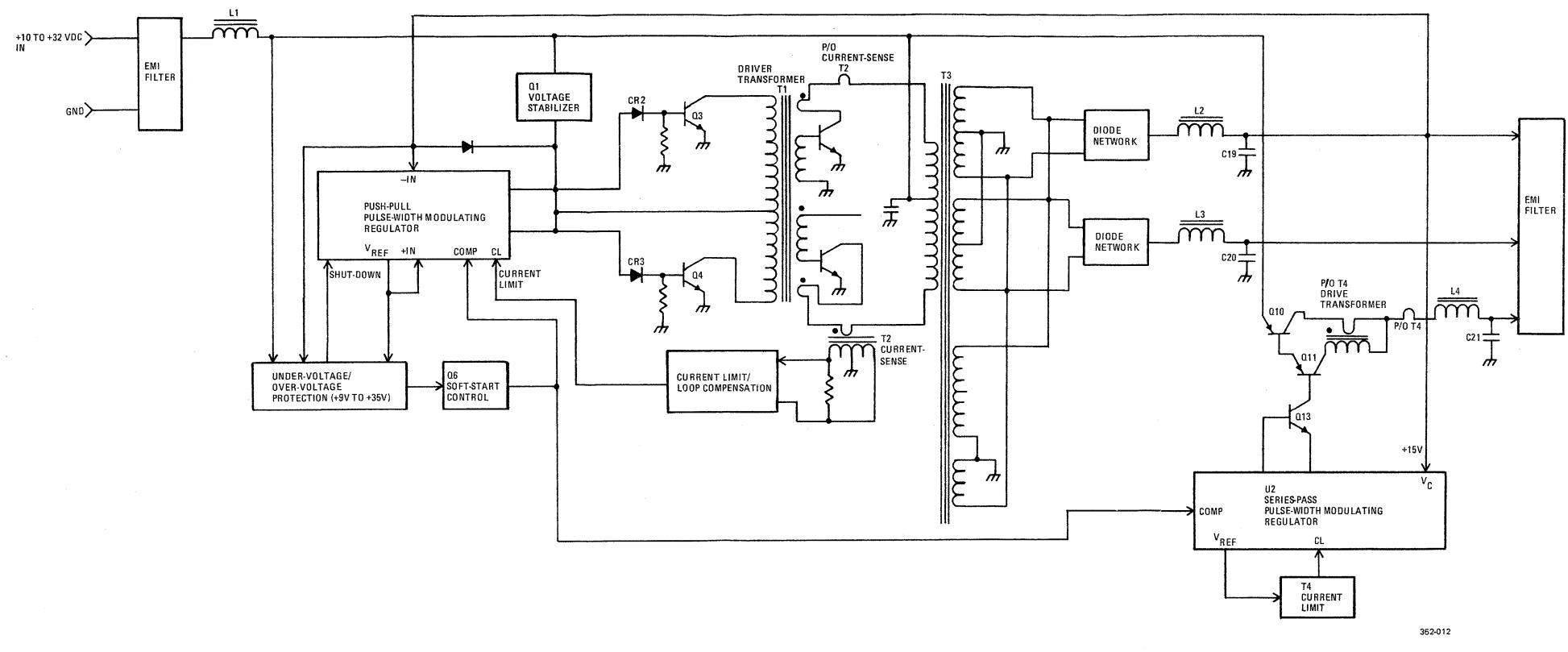

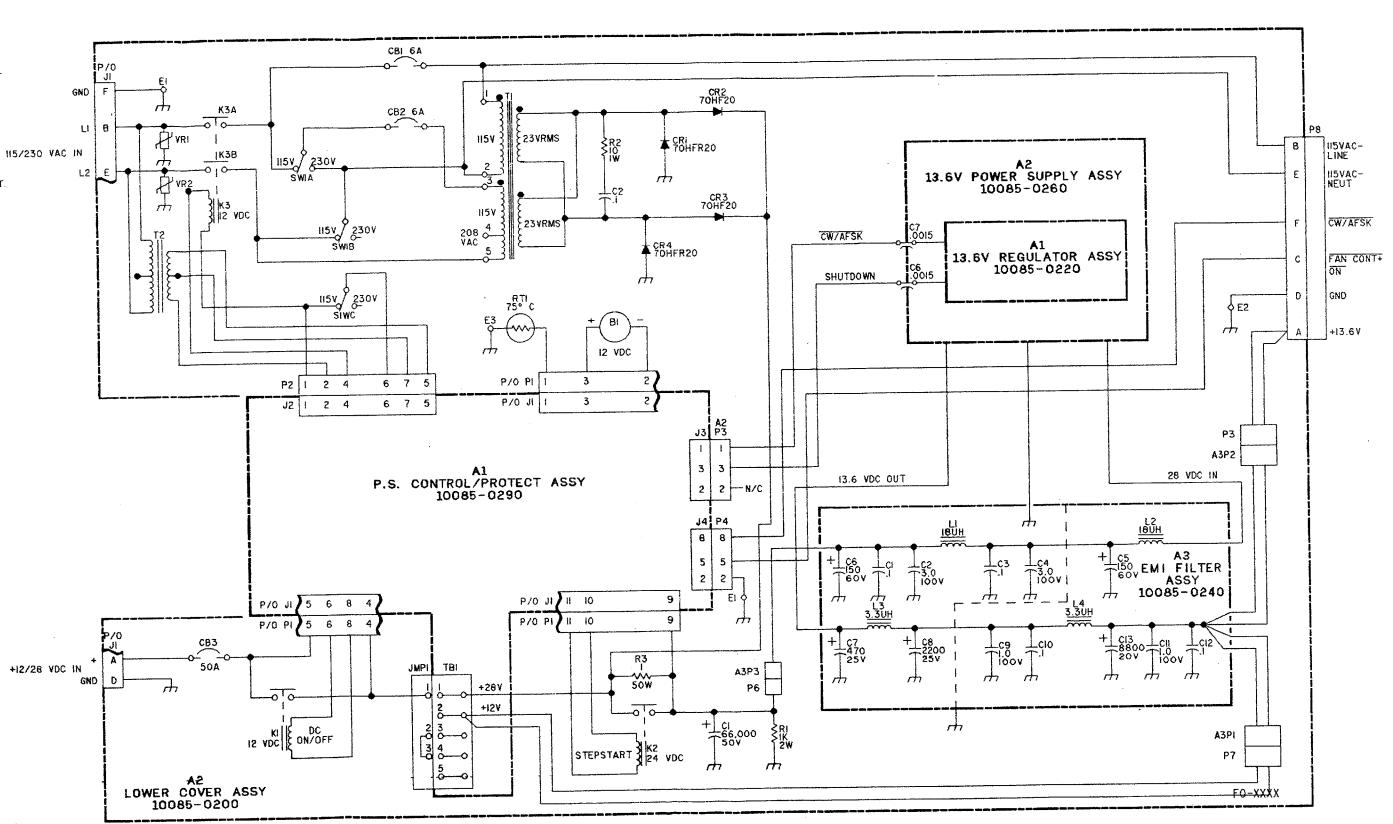

| 5-8.           | Functional Operation and Signal Flow of Power Supply Circuits        | 10 |

| 5-9.           | Introduction                                                         | 14 |

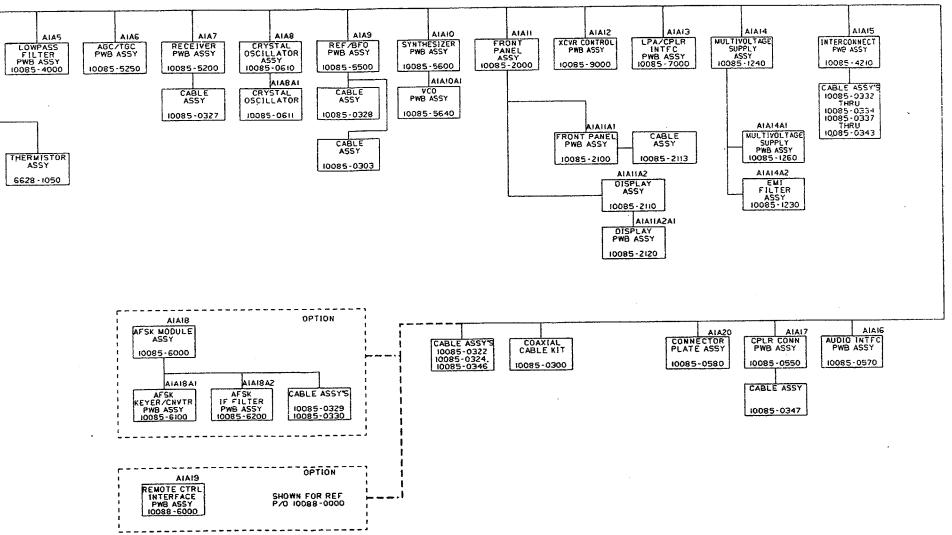

| 5-10.          | Overall Assembly Descriptions                                        | 14 |

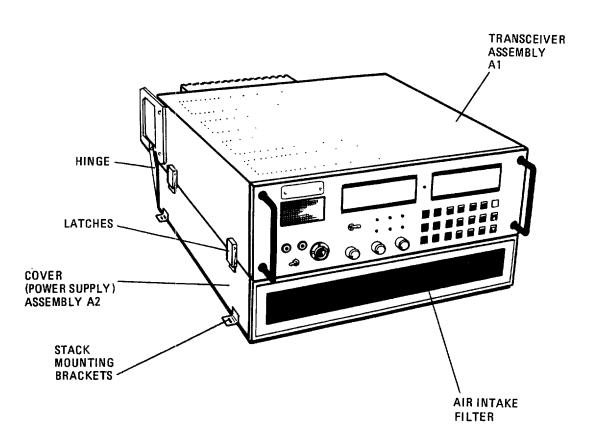

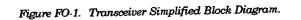

| 5-11.          | Transceiver Assembly A1, 10085-0100                                  |    |

| 5-12.          | Interconnection Cables                                               | 15 |

| 5-13.          |                                                                      | 15 |

| 5-14.          |                                                                      | 15 |

| 5-15.          |                                                                      | 16 |

| 5-16.          |                                                                      | 16 |

| 5-17.          | Detailed Exciter Board Circuit Descriptions                          | 19 |

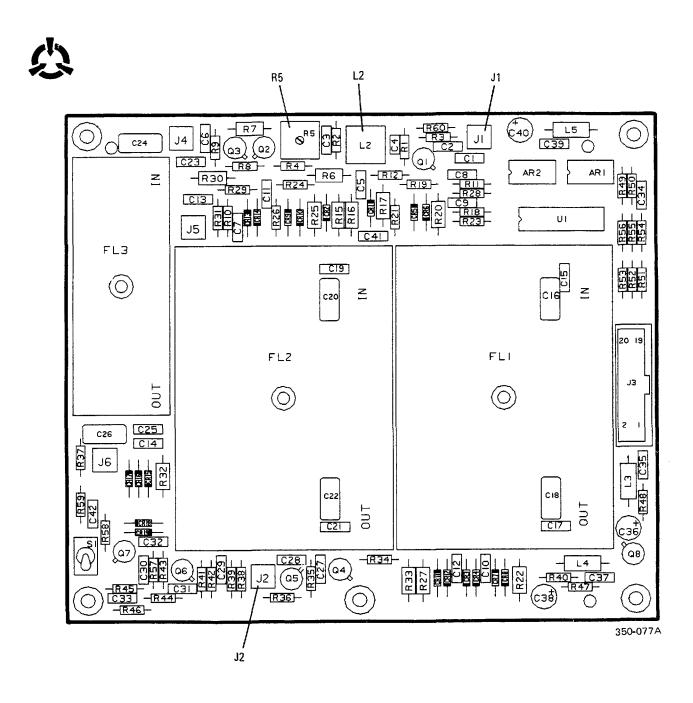

| 5-18           | IF Filter PWB Assembly, A1A2, 10085-5300                             | 28 |

| 5-19.          |                                                                      | 29 |

| 5-19.<br>5-20. | Detailed IF Filter Board Circuit Description                         | 29 |

| 5-20.<br>5-21. |                                                                      |    |

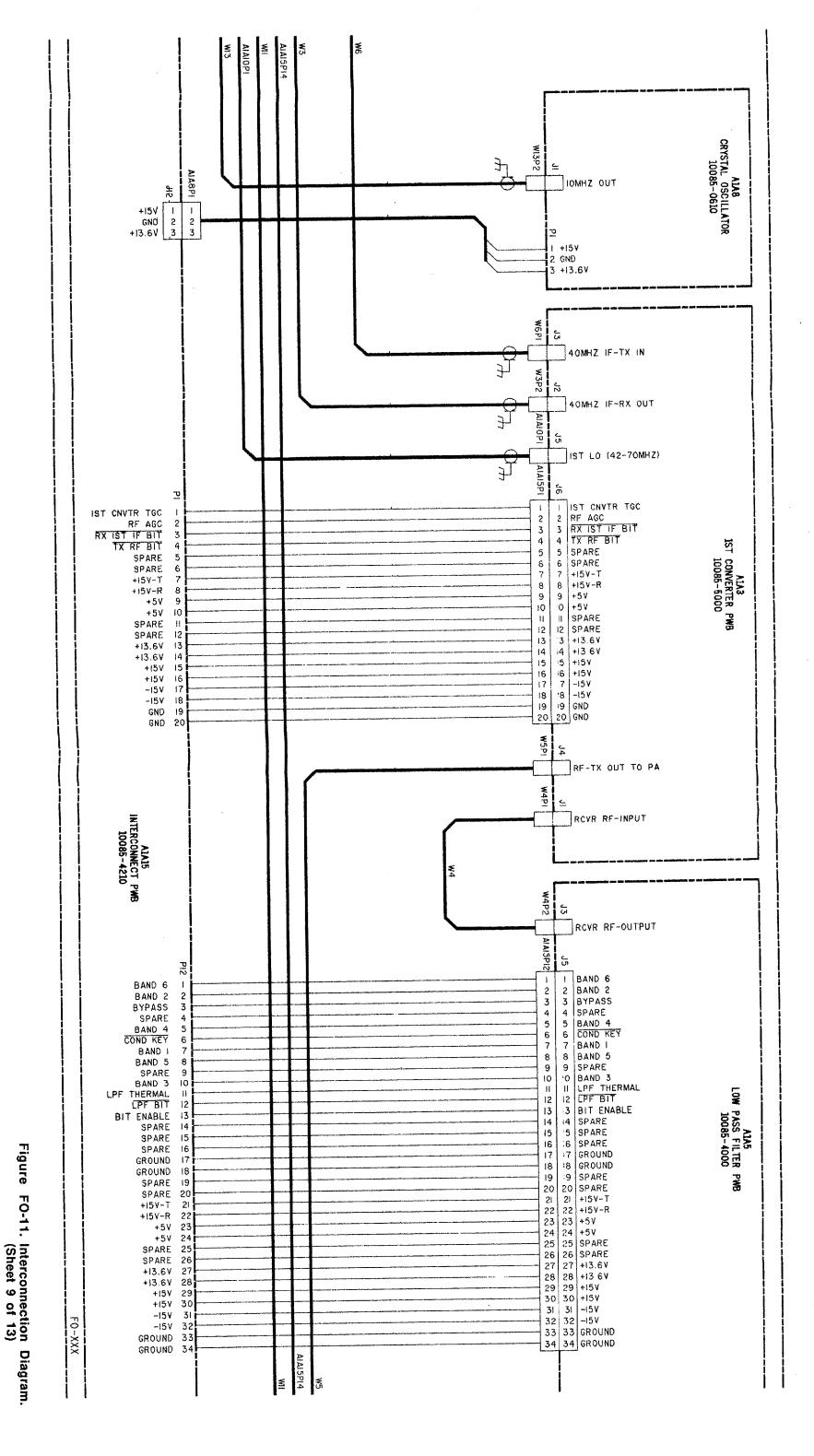

| 5-21.          | Circoliventer Pivot assembly ATAS, 10085-5000                        | 30 |

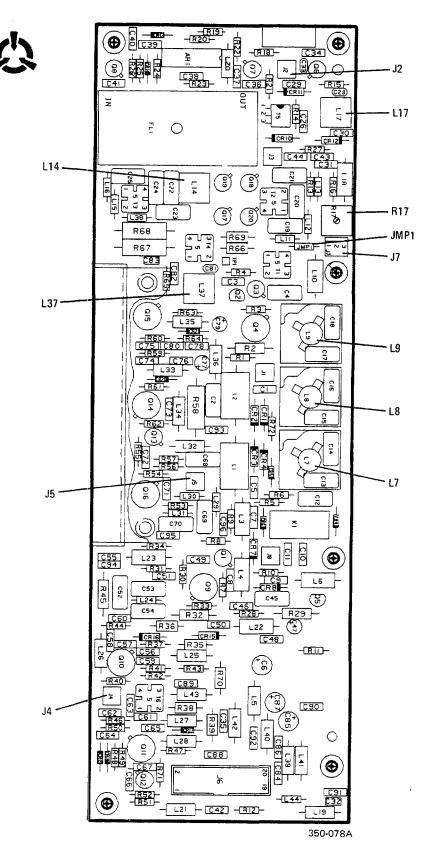

| 5-22.<br>5-23. | Overall First Converter PWB Function.                                | 30 |

|                |                                                                      | 30 |

| 5-24.          |                                                                      | 33 |

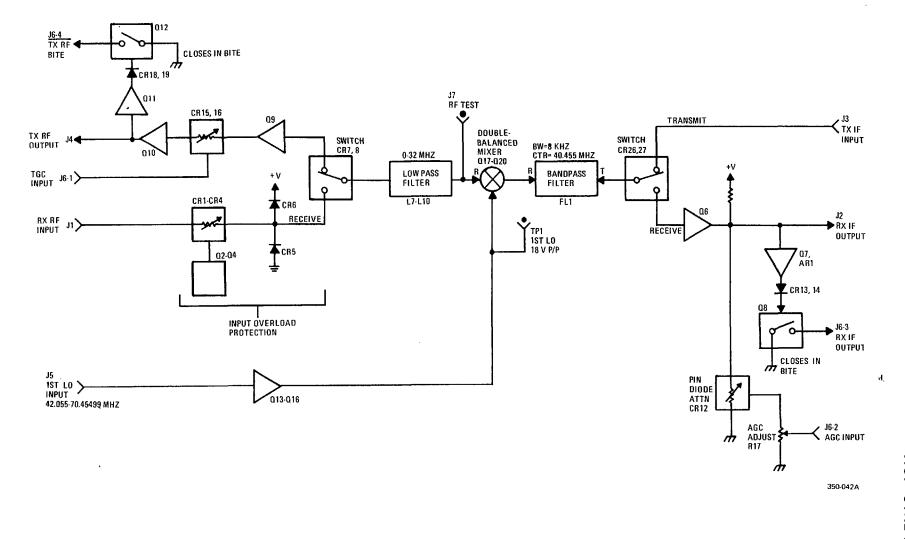

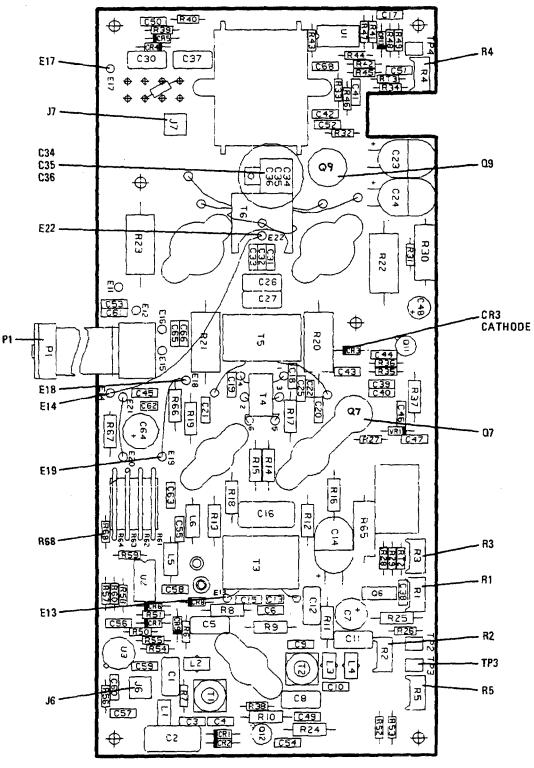

| 5-25.          | Overall 100 WATT PA Assembly Function                                | 33 |

| 5-26.          | Detailed 100 WATT PA Assembly Description                            | 33 |

| 5-27.          |                                                                      | 35 |

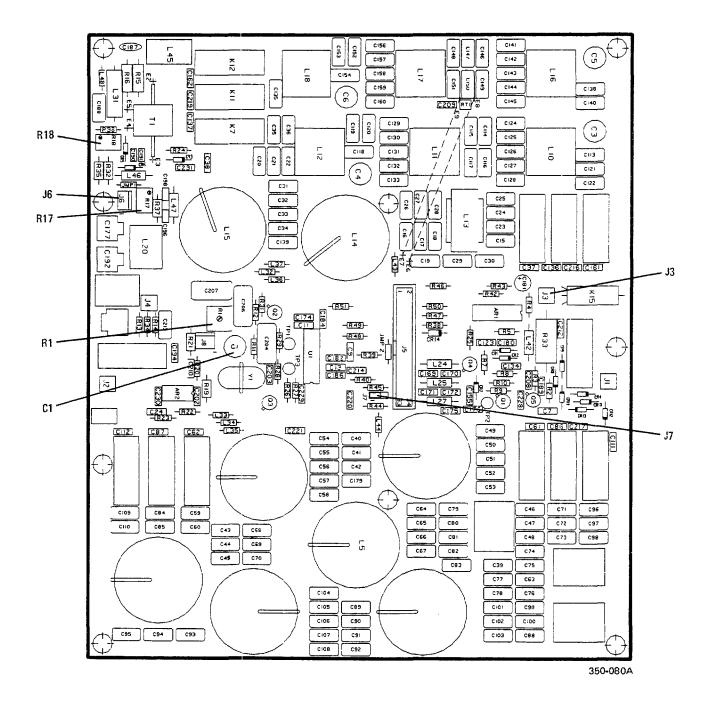

| 5-28.          | Overall Low Pass Filter PWB Function                                 | 35 |

| 5-29.          |                                                                      | 35 |

| 5-30.          | Transmit Signal Path 5-3                                             | 35 |

| 5-31.          | Receive Signal Path                                                  | 36 |

| 5-32.          | Low Pass Filter BIT Functions                                        | 37 |

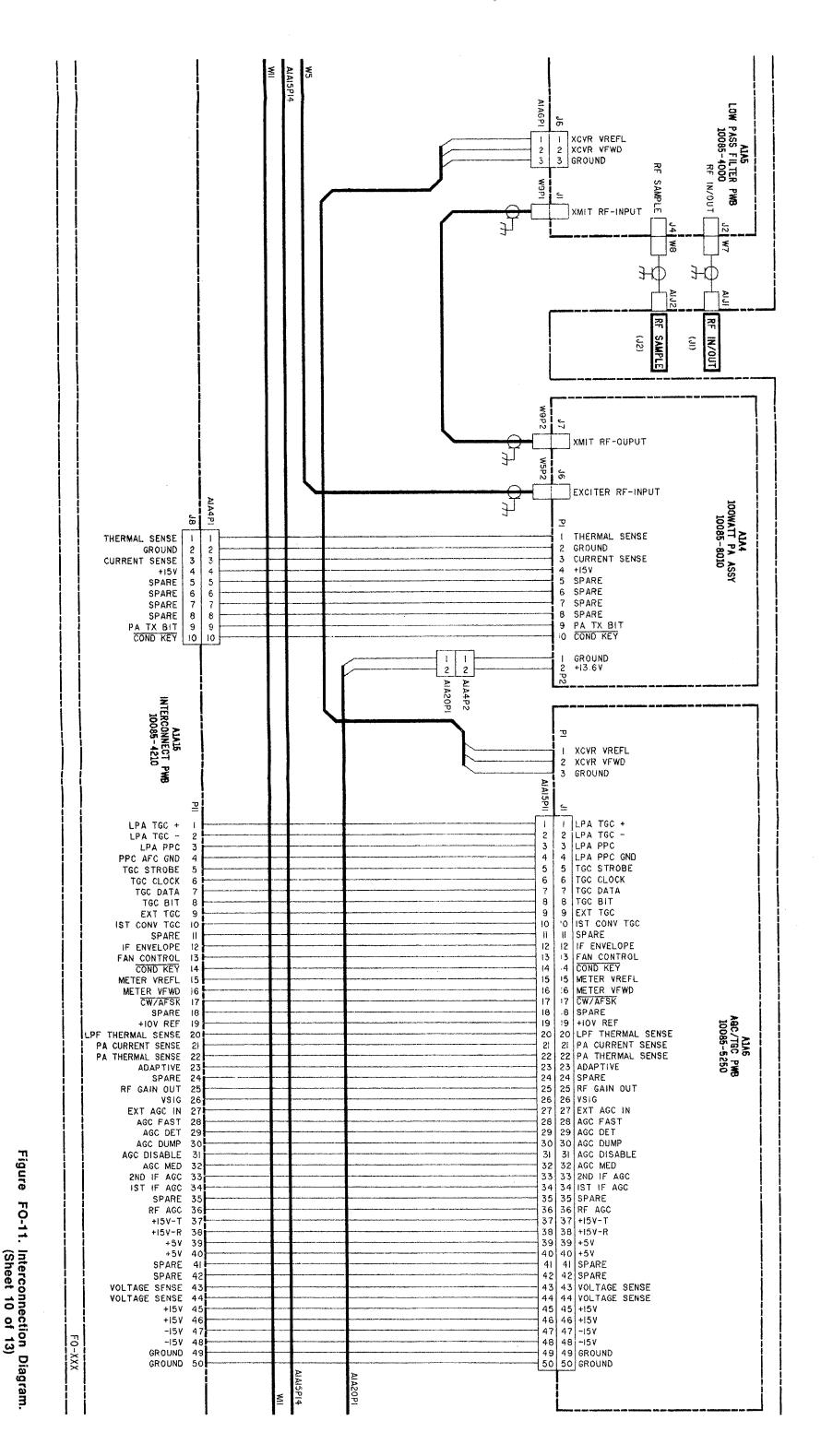

| 5-33.          | AGC/TGC PWB Assembly A1A6, 10085-5250                                | 37 |

| 5-34.          |                                                                      | 37 |

| 5-35.          |                                                                      | 39 |

| 5-36.          |                                                                      | 41 |

| 5-37.          | TGC Operation                                                        |    |

| 5-38.          |                                                                      | 43 |

| 5-39.          |                                                                      | 43 |

| 5-35.<br>5-40. |                                                                      | 50 |

| 5-40.<br>5-41. | Overall Receiver PWB Function                                        | 50 |

|                |                                                                      |    |

| 5-42.          | Overall Receiver PWB Operation.                                      | 50 |

| 5-43.          | Detailed Receiver PWB Circuit Operation                              |    |

| 5-44.          |                                                                      | 56 |

| 5-45.          |                                                                      | 56 |

| 5-46.          | Detailed Crystal Oscillator Circuit Description                      |    |

| 5-47.          | Crystal Oscillator Summary of Specifications                         |    |

| 5-48.          |                                                                      | 56 |

| 5-49.          |                                                                      | 58 |

| 5-50.          |                                                                      | 58 |

| 5-51.          |                                                                      | 58 |

| 5-52.          | Detailed BFO Circuit Operation 5-6                                   |    |

| 5-53.          |                                                                      | 64 |

| 5-54.          |                                                                      | 67 |

| 5-55.          |                                                                      | 67 |

| 5-56.          | Detailed Circuit Operation                                           | 71 |

## TABLE OF CONTENTS (Continued)

#### Section/Para

#### Page

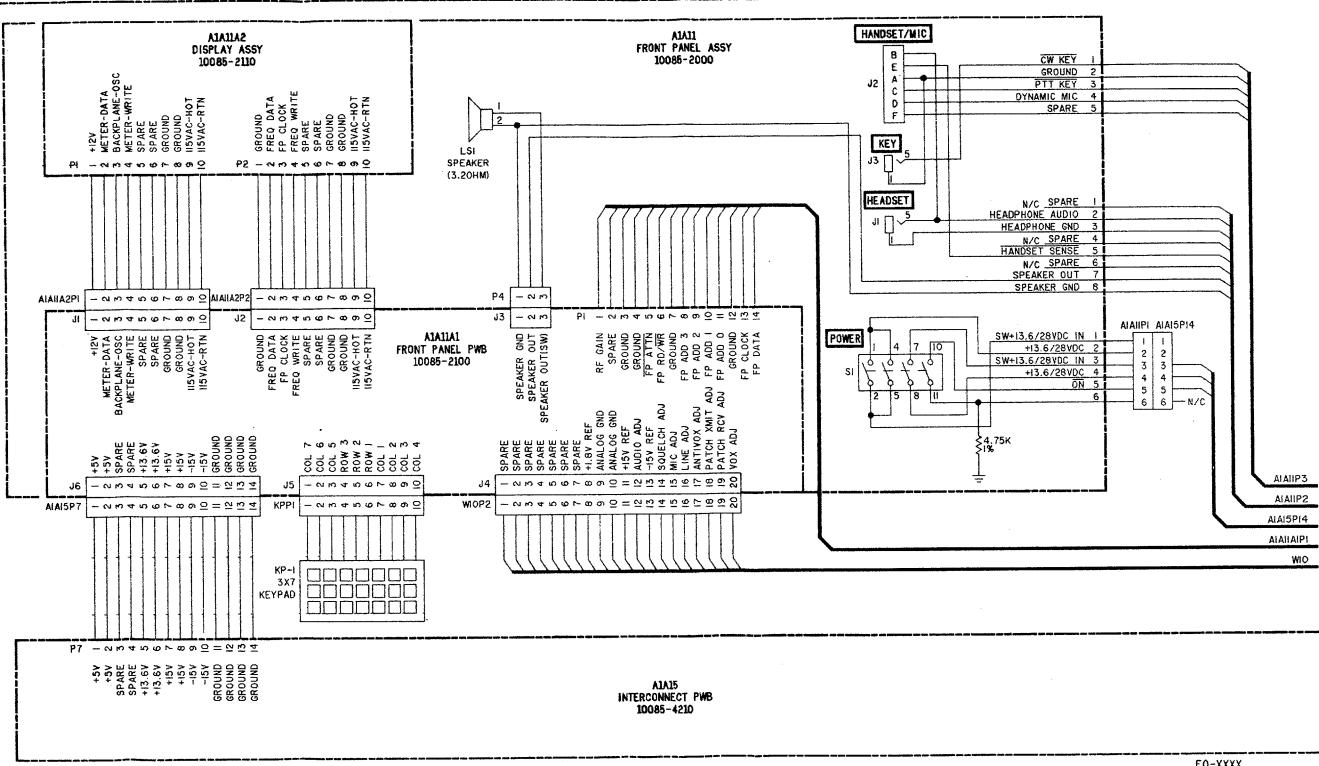

| 5-57.          | Front Panel Assembly A1A11, 10085-2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-75         |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

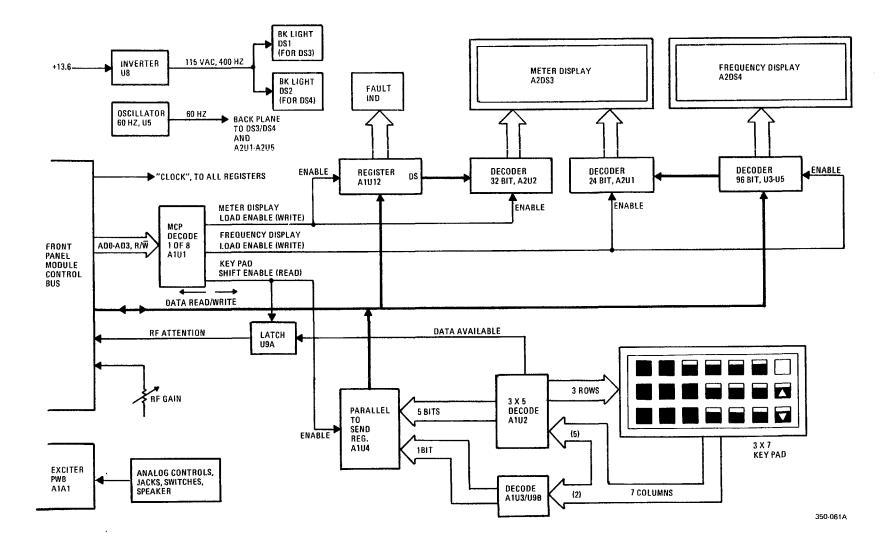

| 5-58.          | Overall Front Panel Assembly Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-75         |

| 5-59.          | Detailed Front Panel Assembly Circuit Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-77         |

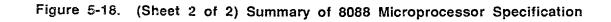

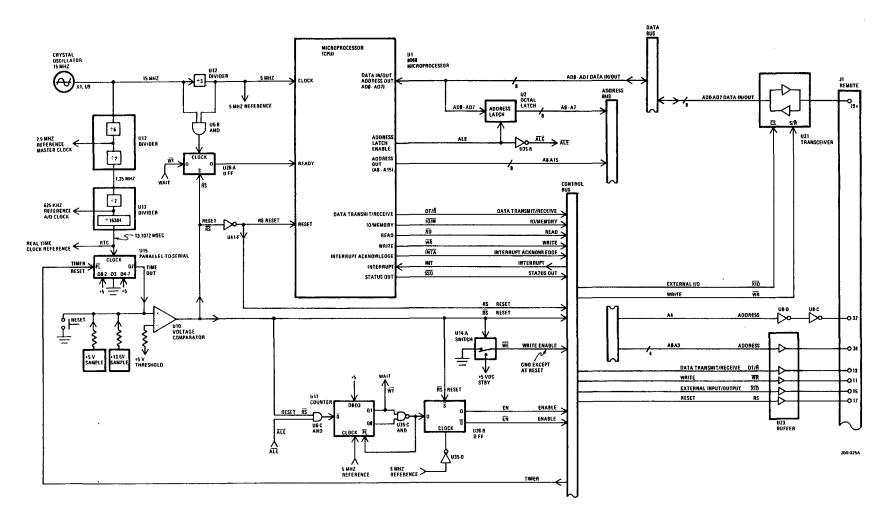

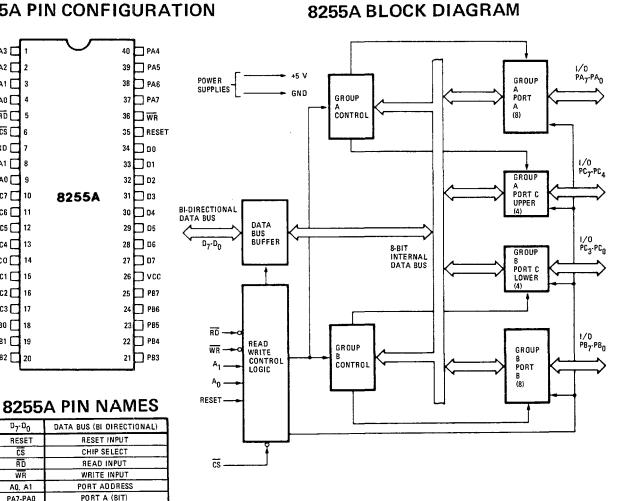

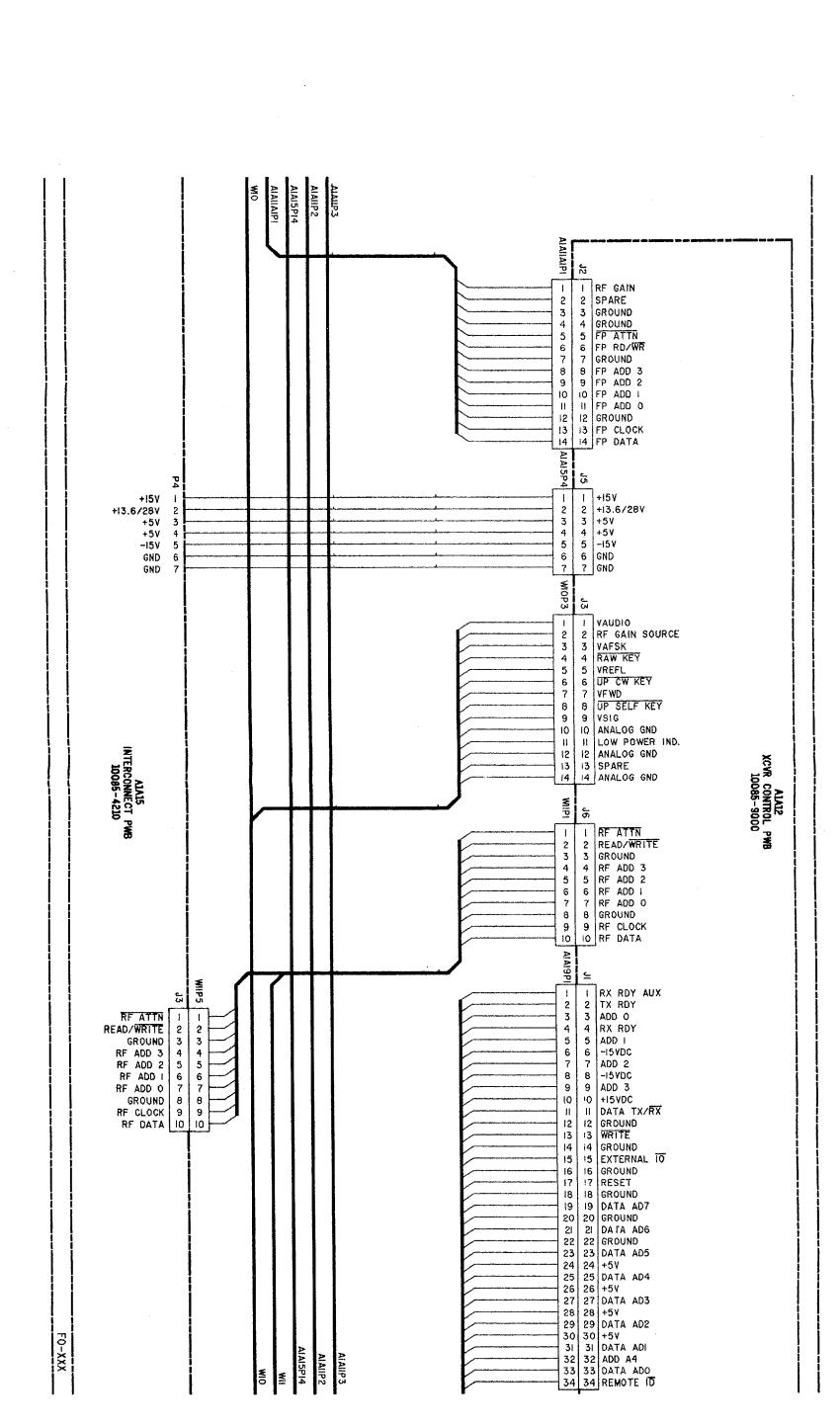

| 5-60.          | Transceiver Control PWB Assembly A1A12, 10085-9000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-78         |

| 5-61.          | Overall Transceiver Control PWB Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-78         |

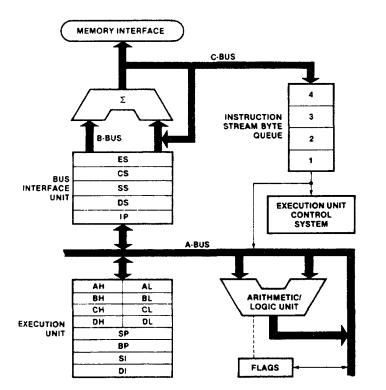

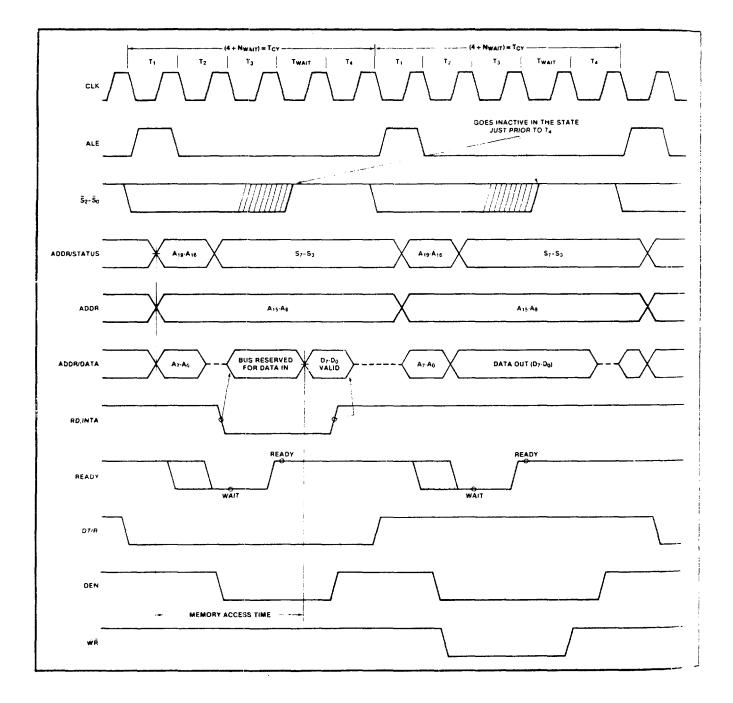

| 5-62.          | Microprocessor, and Related Control Functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-90         |

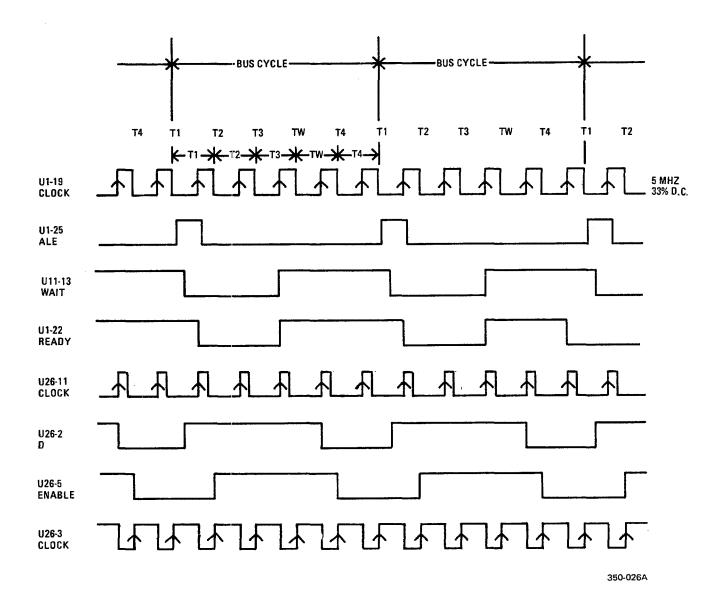

| 5-62.          | Enables for Control Bus Activity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-90         |

|                | Enables for Control bus Activity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-92<br>5-92 |

| 5-64.          | Remote Control Interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| 5-65.          | Input/Output Device Select/Control Logic Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-93         |

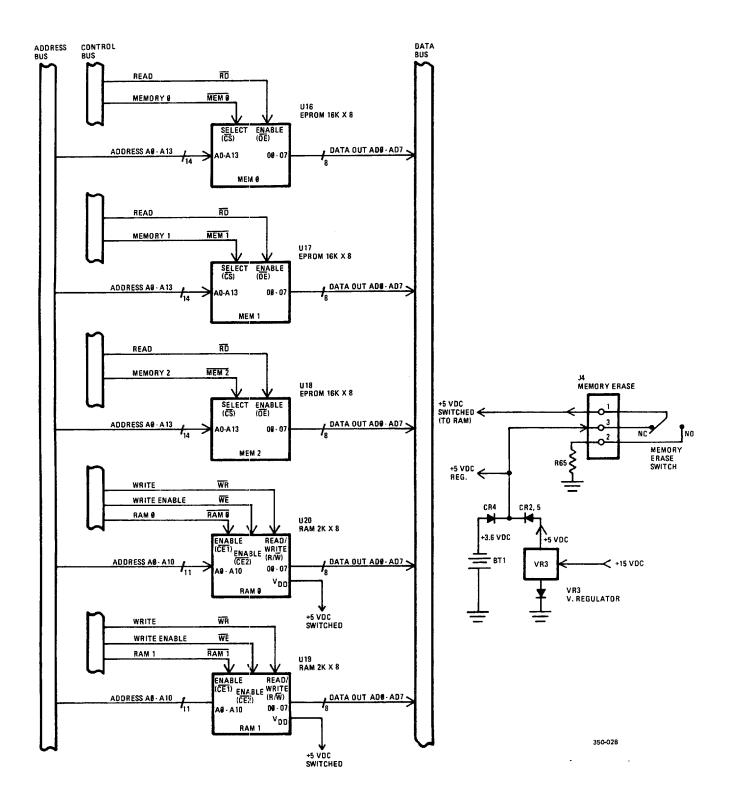

| 5-66.          | Memory Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-96         |

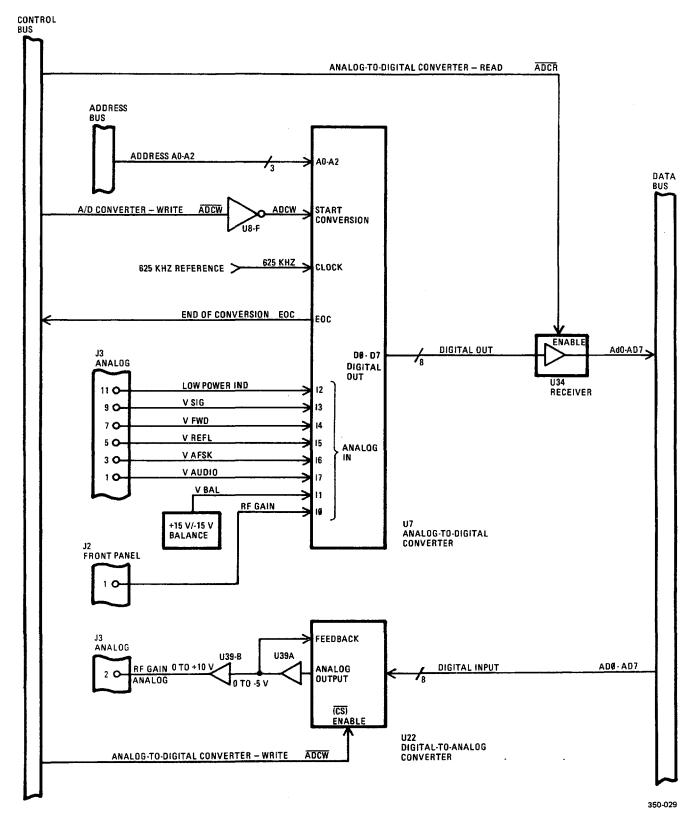

| 5-67.          | Analog-to Digital/Digital-to-Analog Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-98         |

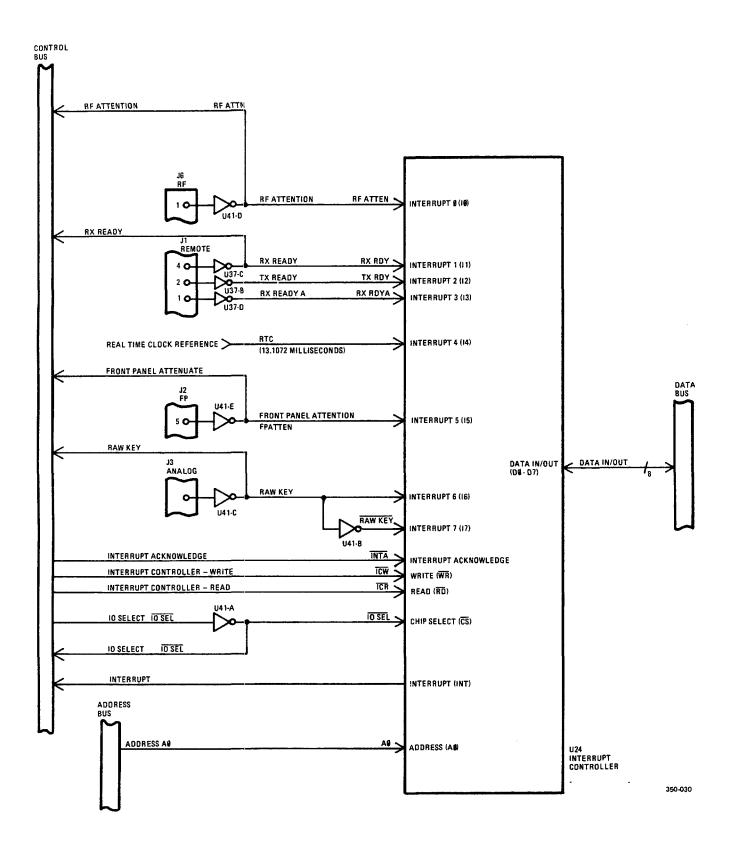

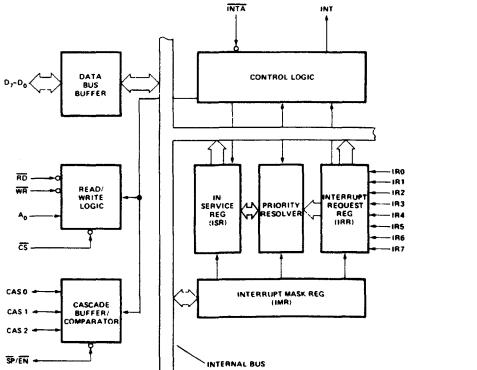

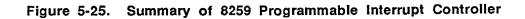

| 5-68.          | Interrupt Controller U24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-99         |

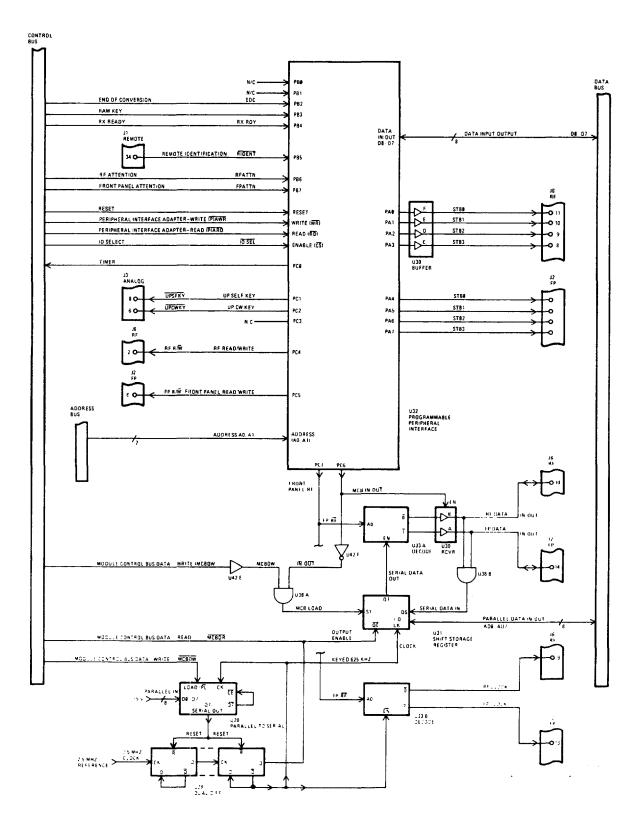

| 5-69.          | Programmable Peripheral Interface U32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-100        |

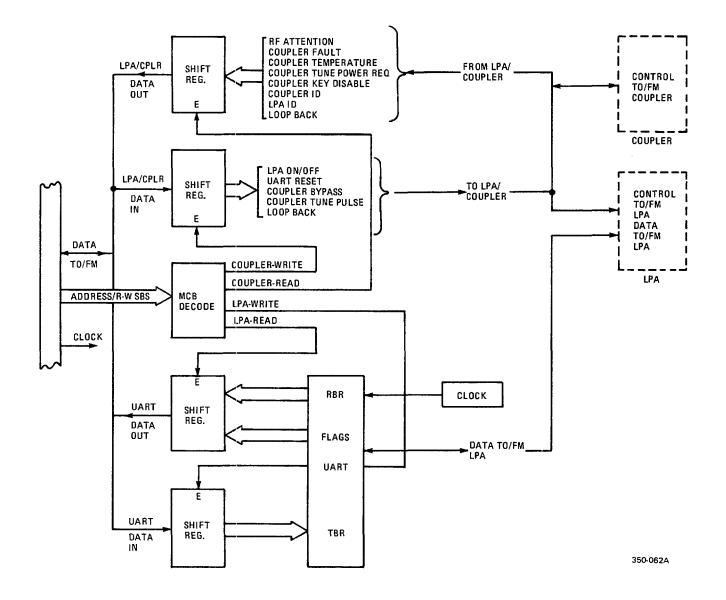

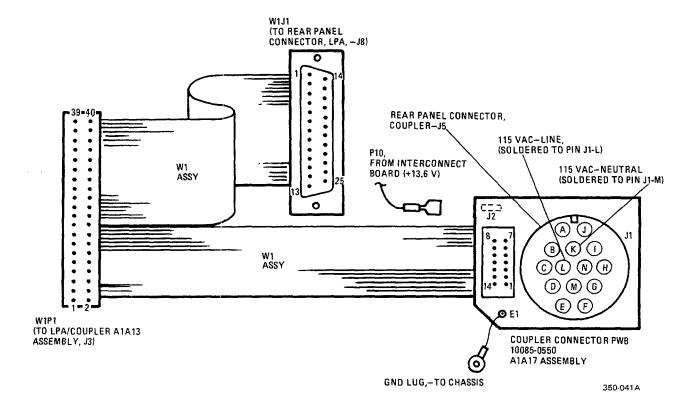

| 5-70.          | LPA/Coupler Interface PWB Assembly A1A13, 10085-7000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-103        |

| 5-71.          | Overall LPA/Coupler Interface PWB Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-103        |

| 5-72.          | Detailed LPA/Coupler Interface PWB Board Circuit Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-105        |

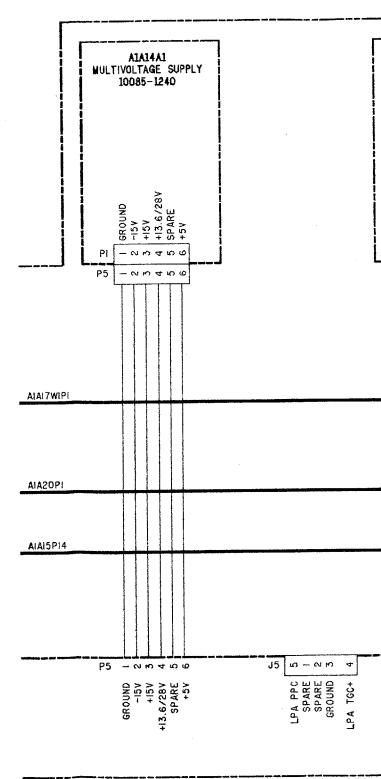

| 5-73.          | Multivoltage Converter Assembly A1A14, 10085-1240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-106        |

| 5-74.          | Overall Multivoltage Converter Assembly Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-107        |

| 5-75.          | Detailed Multivoltage Converter Assembly Circuit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-107        |

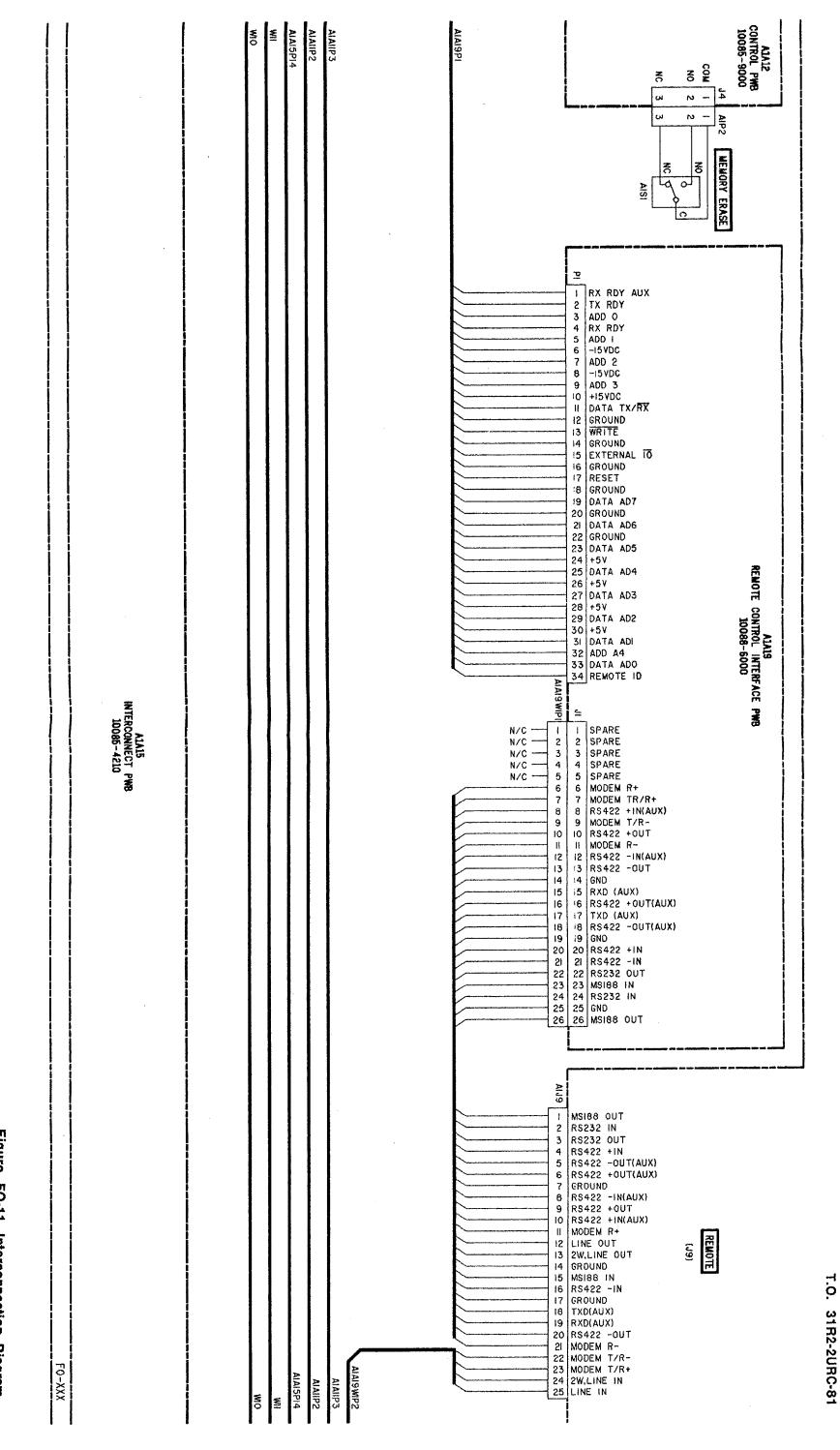

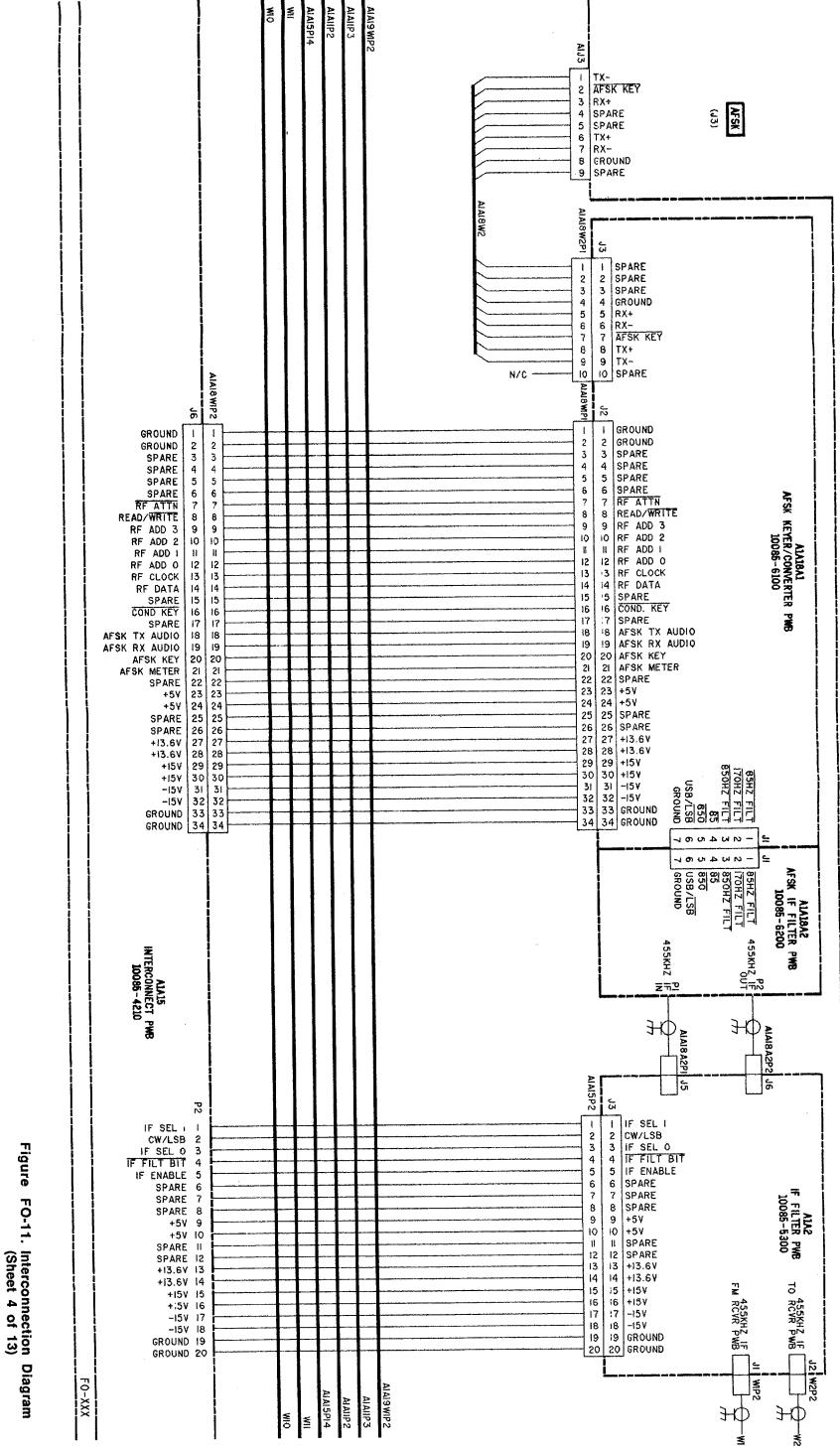

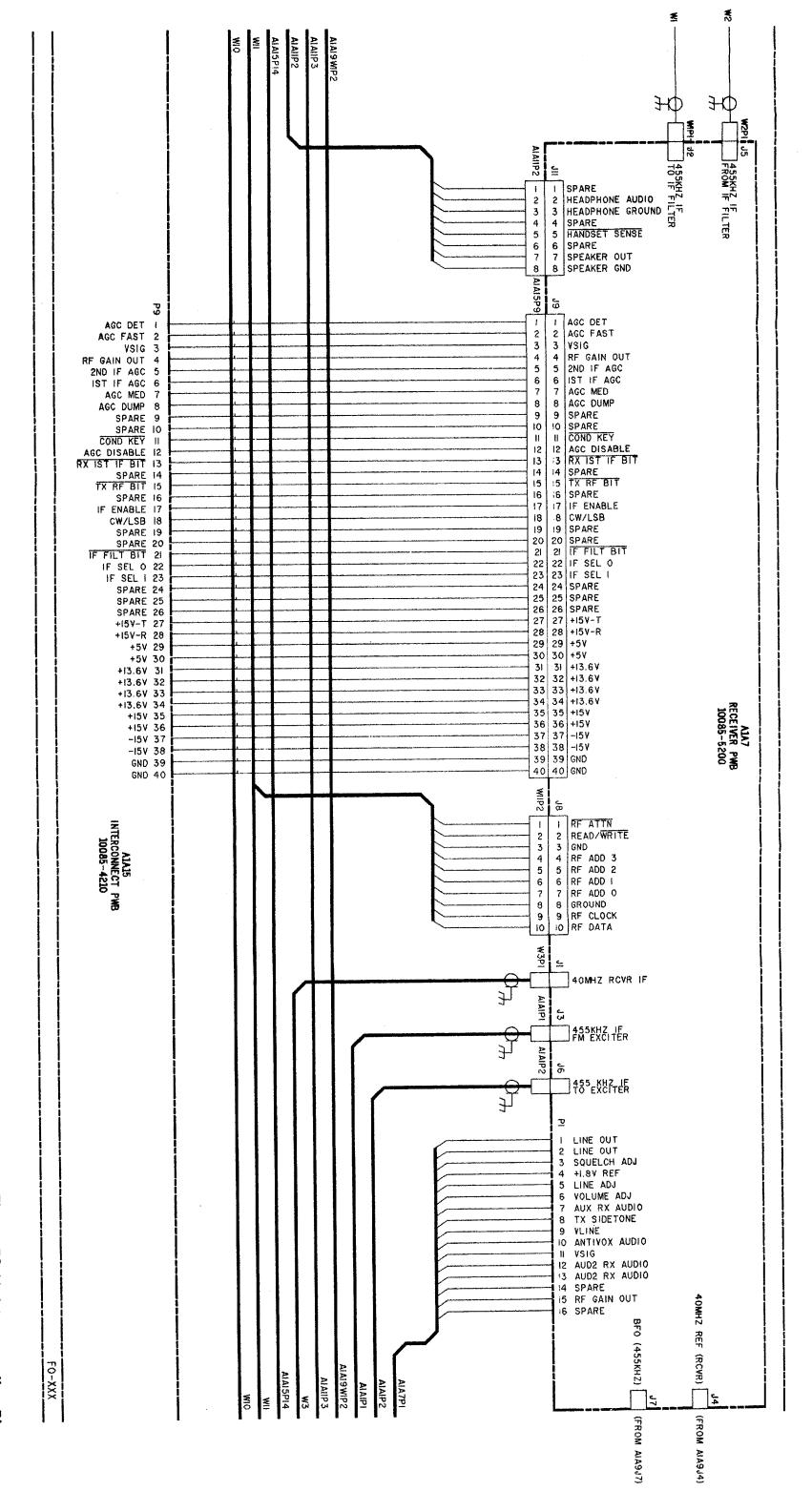

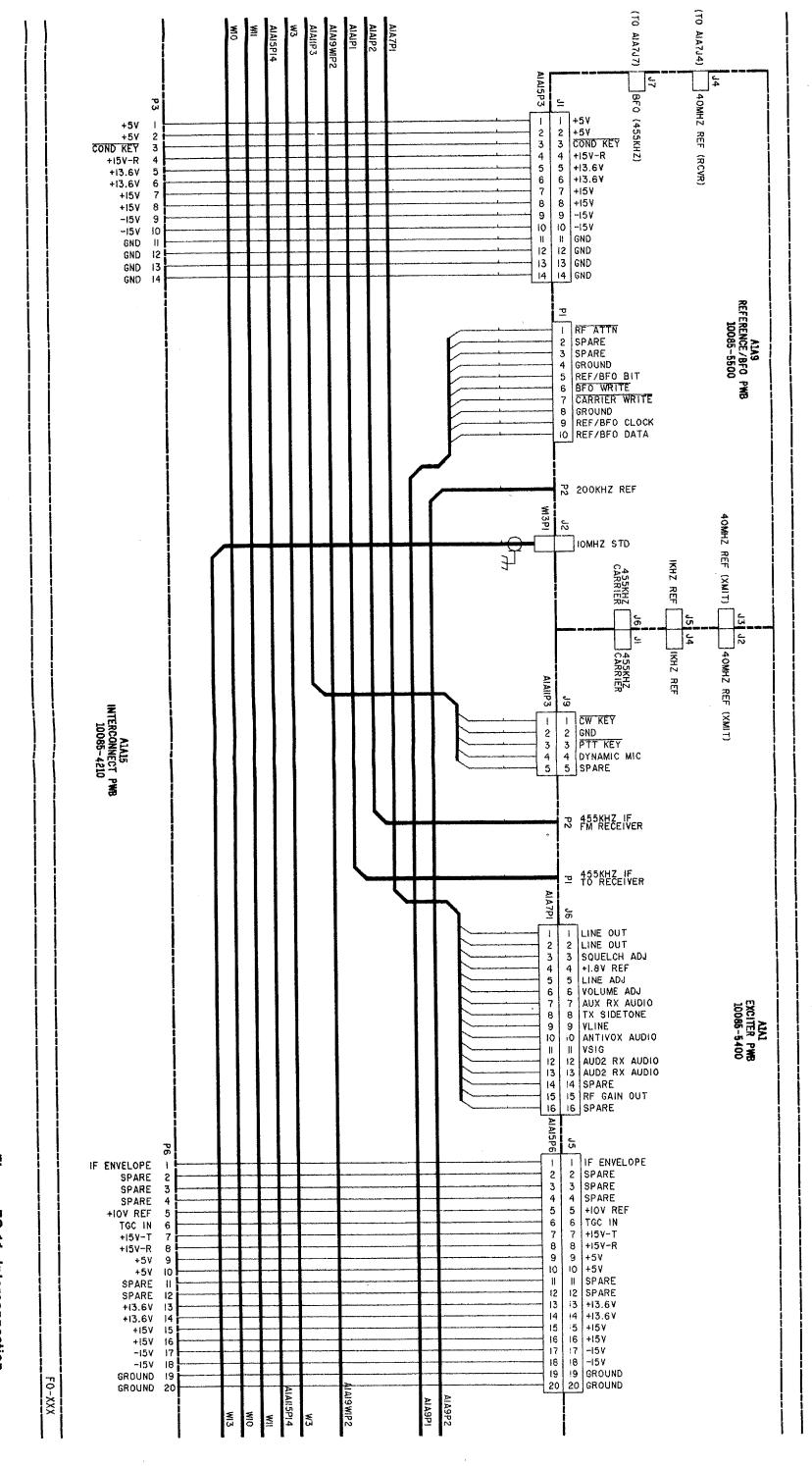

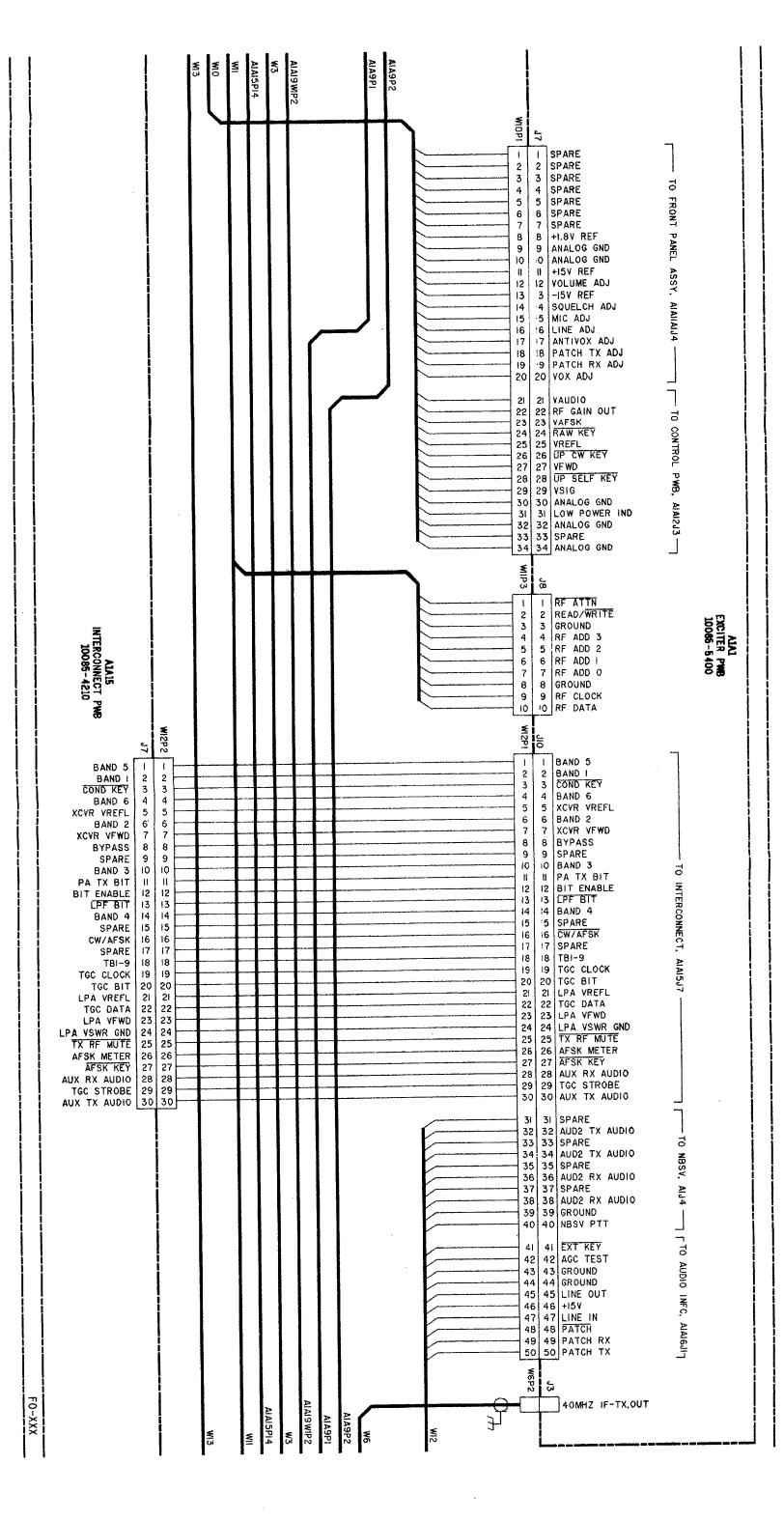

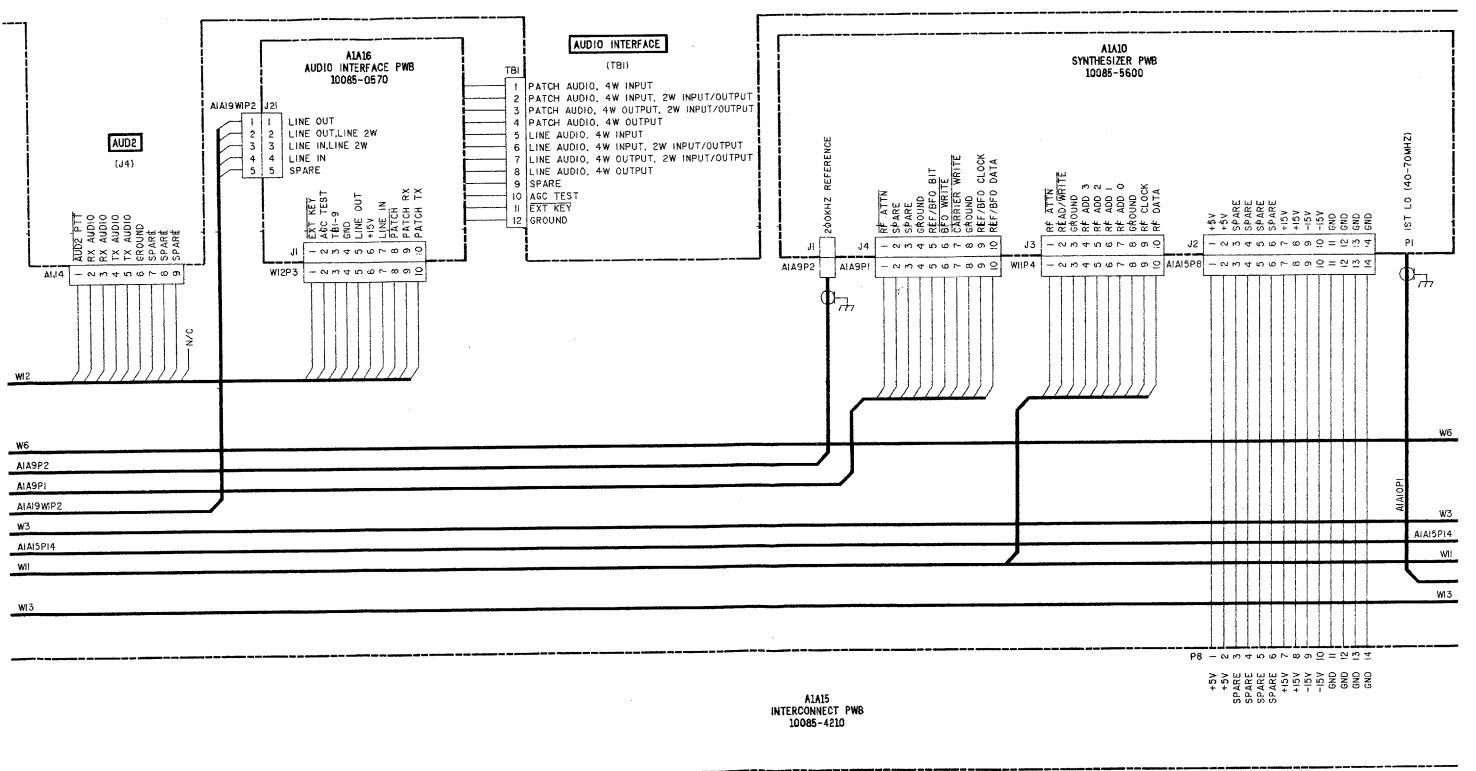

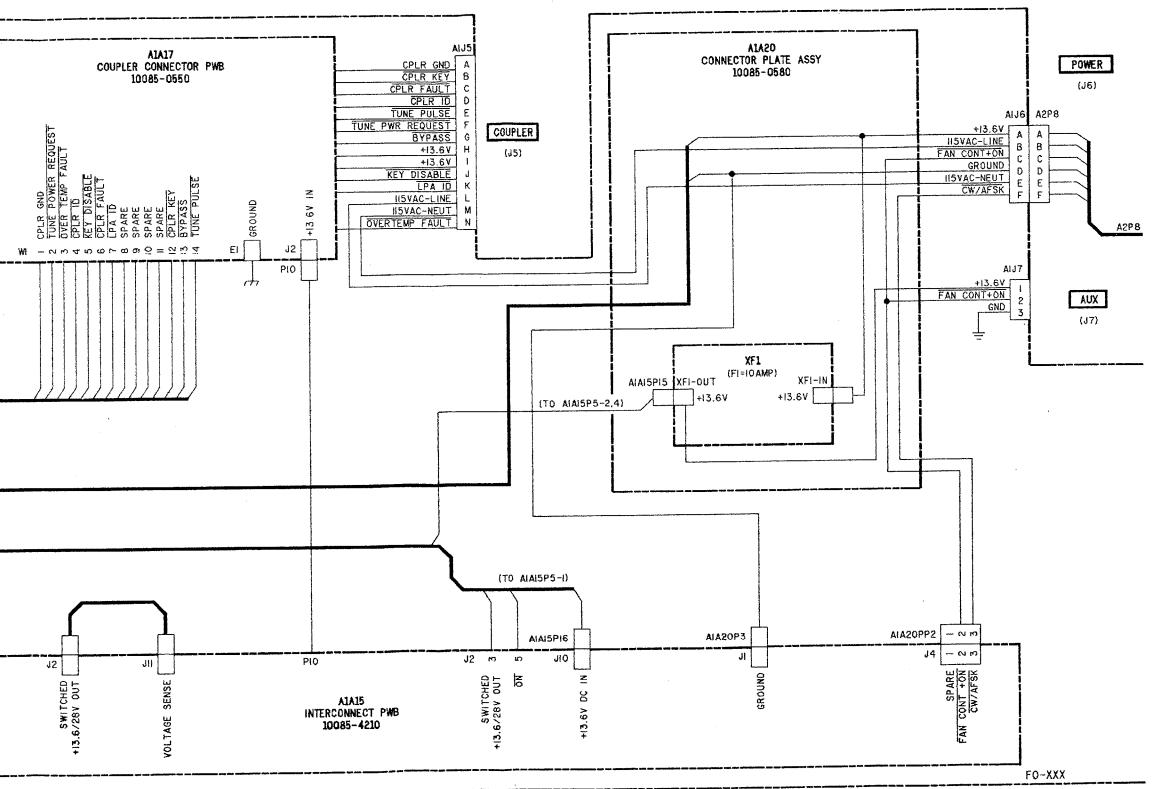

| 5-76.          | Interconnect PWB Assembly A1A15, 10085-4210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-109        |

| 5-77.          | Overall Interconnect PWB Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-110        |