0056-00-419-8000

INSTRUCTION BOOK

# RECEIVER, RADIO AN/GRR-23 and AN/GRR-24

VOLUME 2

EQUIPMENT CONTRACTOR INTERNATIONAL TELEPHONE AND TELEGRAPH CORPORATION FORT WAYNE, INDIANA F04606-74-C-0990 AND F34601-68-C-4219

> INSTRUCTION BOOK CONTRACTOR UNIFIED INDUSTRIES INCORPORATED ALEXANDRIA, VIRGINIA FA76WAI-604

> > MADE FOR

U.S. DEPARTMENT OF TRANSPORTATION FEDERAL AVIATION ADMINISTRATION

| HANGE | SUPPLEMENTS |          |      |                                       | CHANGE      | su  | PPLEMEN | rs |              |

|-------|-------------|----------|------|---------------------------------------|-------------|-----|---------|----|--------------|

| TO    |             | Chy      | Chap | OPTIONAL USE                          | TO<br>BASIC |     |         |    | OPTIONAL USE |

|       |             |          | ,    |                                       |             |     |         |    |              |

|       |             |          |      |                                       | · ·         |     |         |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

|       |             | 1        |      |                                       |             |     |         |    | ·········    |

|       |             | 1        |      | · ·                                   |             |     |         |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

|       |             |          | ,    |                                       |             |     |         |    | ······       |

|       | -           |          |      | <u> </u>                              |             |     | · -· -  |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

|       |             | <u> </u> |      | 1                                     |             |     |         |    |              |

|       |             |          |      |                                       | × /         |     |         |    |              |

|       |             |          |      |                                       | /           |     |         |    |              |

|       |             |          |      | · / /                                 |             |     |         |    | <u></u>      |

|       |             | -        |      |                                       |             |     |         |    |              |

|       |             |          |      | / /                                   |             |     |         |    |              |

|       |             |          |      | <u>/</u>                              |             |     |         |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

|       | <b>.</b>    |          |      | 0 }-/                                 |             |     |         |    |              |

|       |             |          |      | <u>}</u>                              |             | ļ ļ |         |    |              |

|       |             |          |      | /                                     |             |     |         |    |              |

|       |             |          |      | · · · · · · · · · · · · · · · · · · · |             |     |         |    |              |

|       |             |          | /    |                                       |             |     |         |    |              |

|       |             |          |      |                                       |             |     |         |    |              |

| ĺ     |             |          |      |                                       |             |     |         |    |              |

|       |             |          | /    |                                       |             |     |         |    |              |

|       |             | /        |      |                                       |             |     |         |    |              |

|       |             |          |      | · · · · · · · · · · · · · · · · · · · |             |     |         |    |              |

|       |             | 1        |      |                                       |             |     |         |    |              |

|       |             | ¥        |      |                                       |             |     |         |    | <u> </u>     |

6620

.

# AF P 6500.1 CHG 361 Chap 356 1/28/83

### VOLUME 2

#### TABLE OF CONTENTS

| Paragraph                         | Page |

|-----------------------------------|------|

| Functional Index.                 | v    |

| Circuit Identifier Codes          | vi   |

| Explanation of Symbols and Shades | vii  |

# **SECTION 11. DIAGRAMS**

| 11.1 | Introduction                                | 11-1 |

|------|---------------------------------------------|------|

| 11.2 | Use of Subassembly Schematic Diagrams       | 11-1 |

| 11.3 | Shaded Blocked Diagrams and Texts           |      |

| 11.4 | Shaded Blocked Schematic Diagrams and Texts |      |

# LIST OF ILLUSTRATIONS

# Figure

\*

#

#### Page

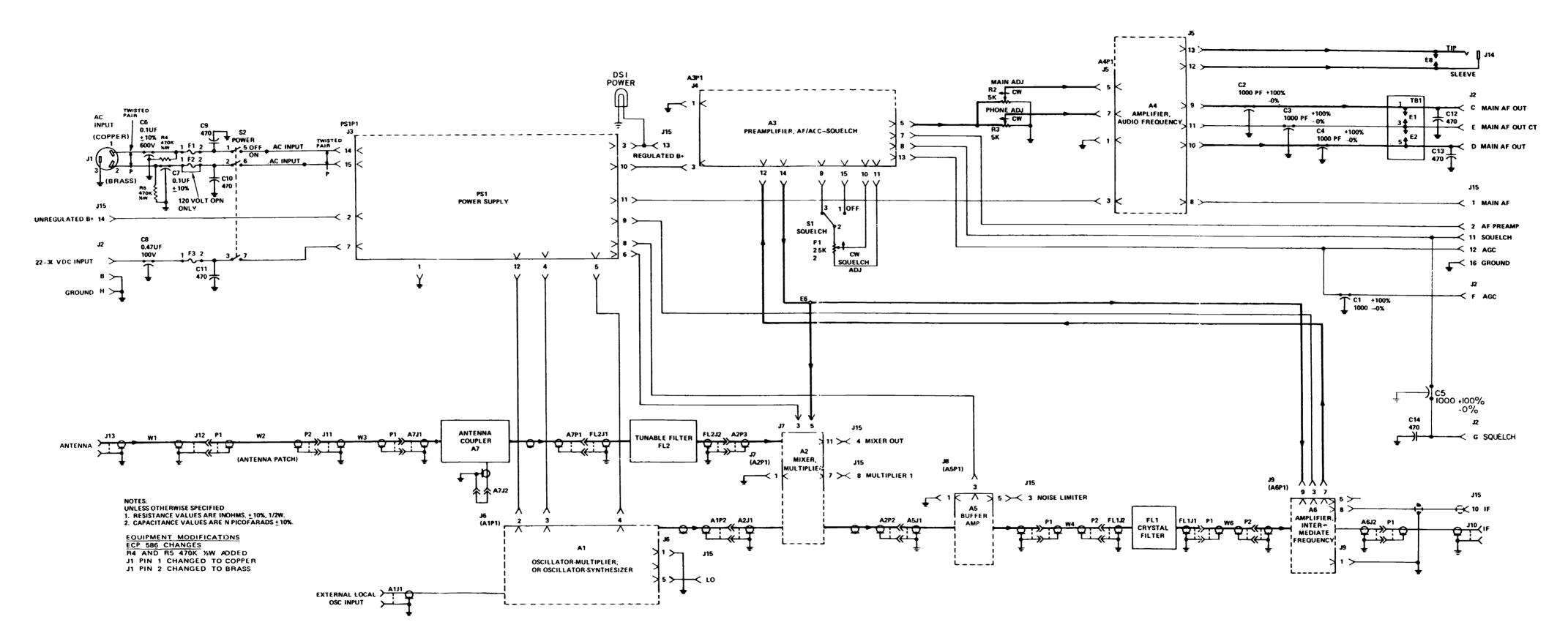

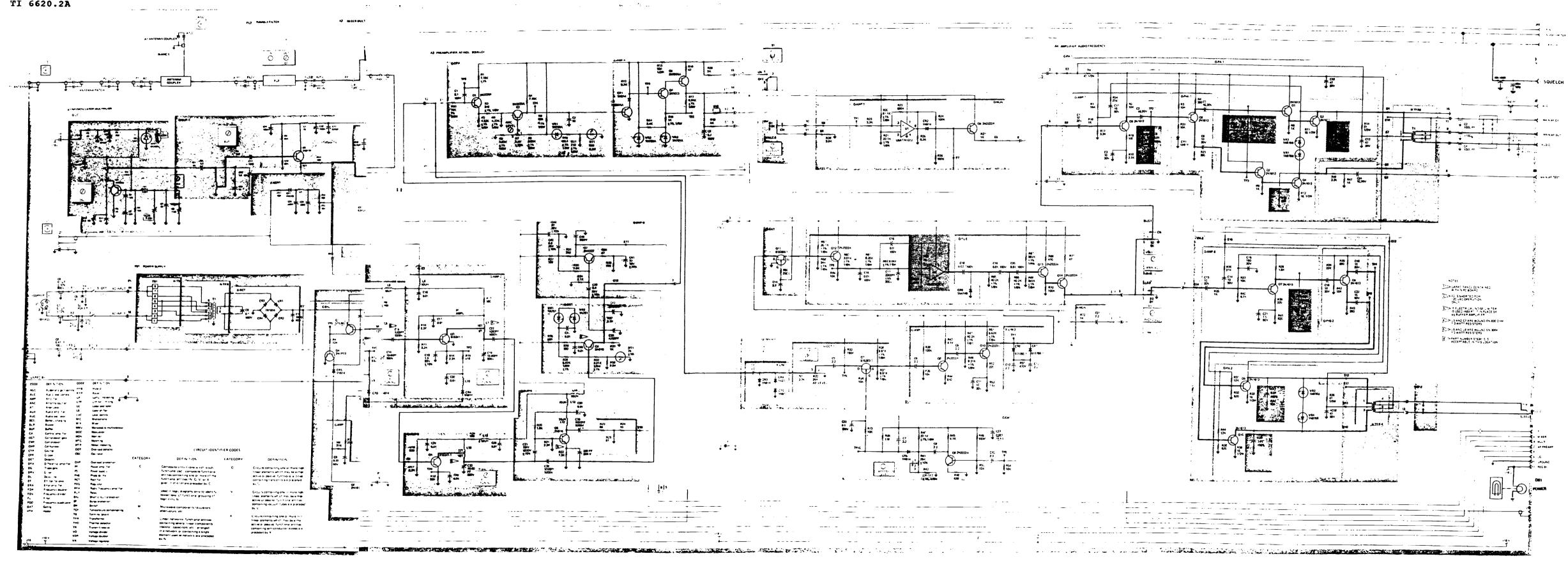

| 11-1   | VHF/UHF Receiver Schematic                                             | 11-5  |

|--------|------------------------------------------------------------------------|-------|

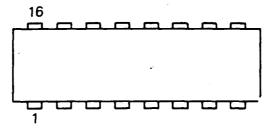

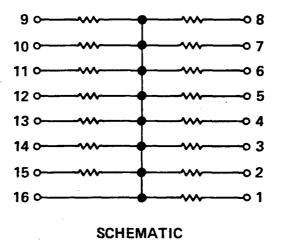

| 11-2   | Fixed Resistor Network Integrated Circuit (509435-1)                   | 11-7  |

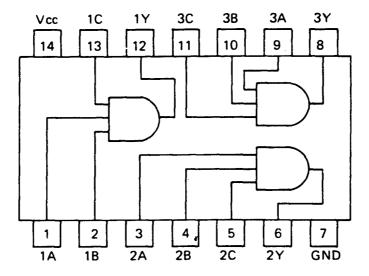

| 11-3   | Triple Three-Input Positive AND Gate Integrated Circuit (SN54H11J-00)  | 11-8  |

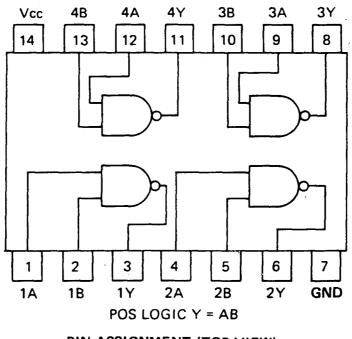

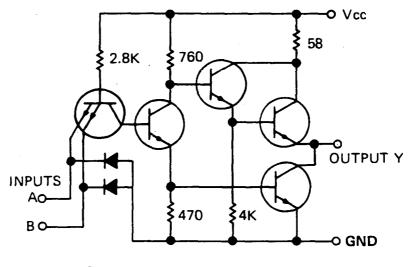

| 11-4   | Quadruple Two-Input Positive NAND Gate Integrated Circuit (SN5400J-00) | 11-9  |

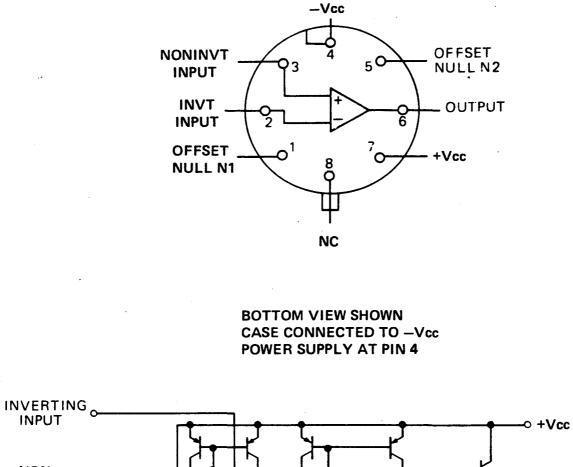

| 11-5   | Operational Amplifier Integrated Circuit (SN52741L-00)                 | 11-10 |

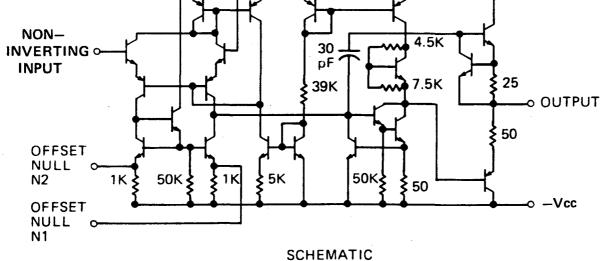

| 11-6   | Operational Amplifier Integrated Circuit (LM101AH)                     | 11-11 |

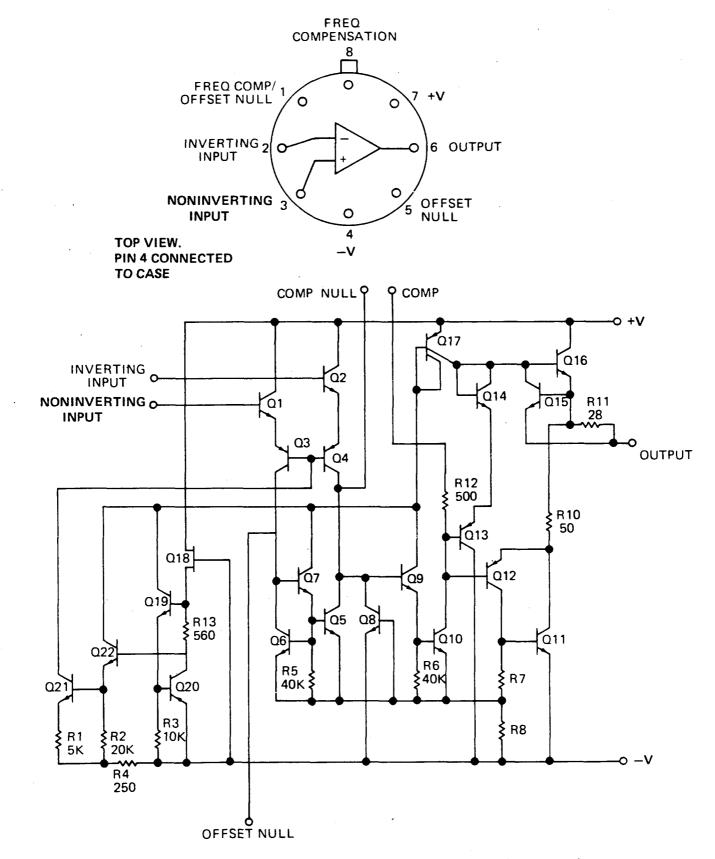

| 11-7   | Switching Regulator Integrated Circuit (PIC600)                        | 11-12 |

| 11-8   | Transistor Array Integrated Circuit (CA3118T)                          | 11-13 |

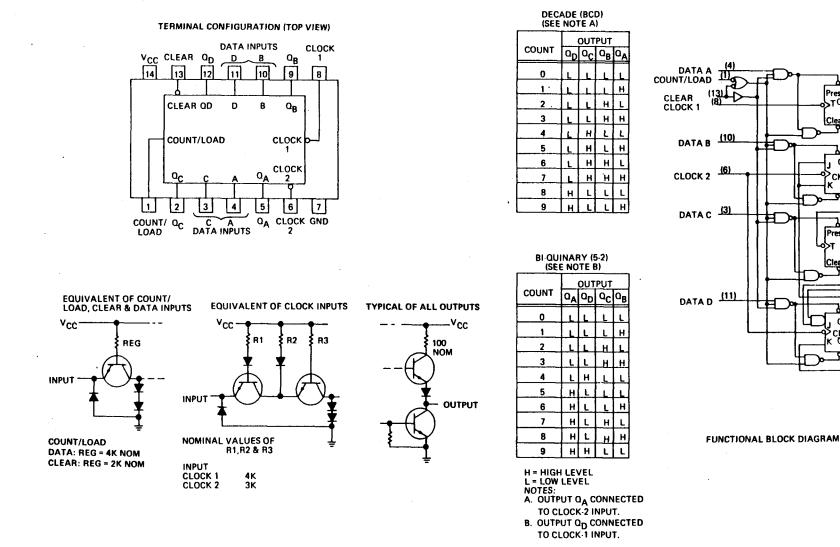

| 11-9   | High-Speed Counter Integrated Circuit (SN54196J-00).                   | 11-14 |

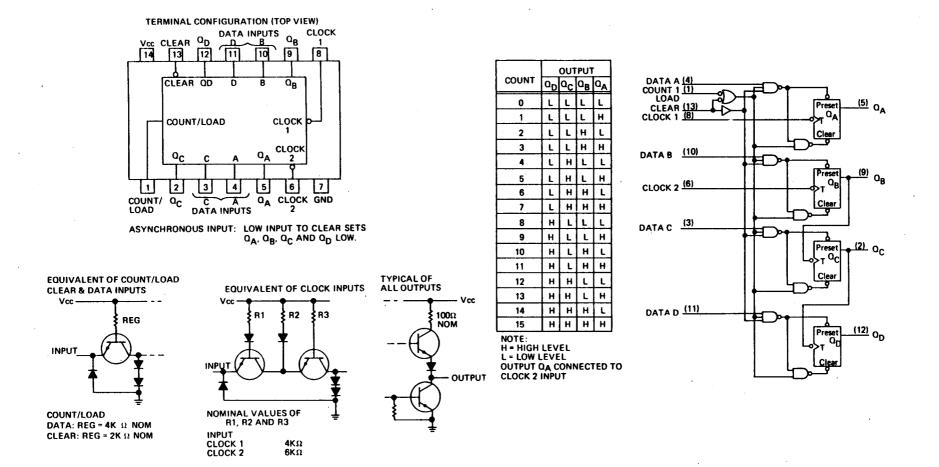

| 11-10  | High-Speed Counter Integrated Circuit (SN54197J-00)                    | 11-15 |

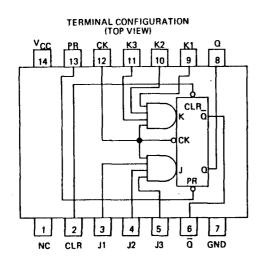

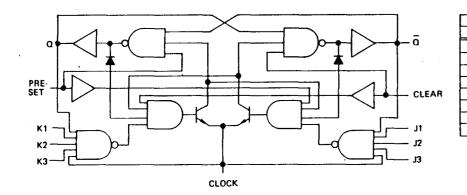

| 11-11  | Edge-Triggered J-K Flip Flop Integrated Circuit (SN54H102J-00)         | 11-16 |

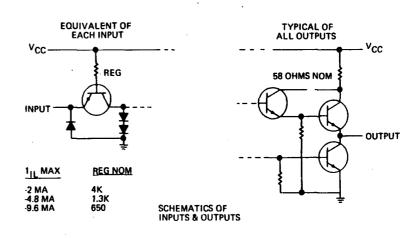

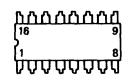

| 11-12  | Dual Master-Slave (D-Type) Flip Flop Integrated Circuit (MC10531L)     | 11-17 |

| 11-13  | Crystal Oscillator A1 G1 (This figure deleted).                        | 11-18 |

| 11-14  | Crystal Oscillator A1 G2 (This figure deleted)                         | 11-20 |

| 11-15  | Oscillator-Multiplier A1(M)                                            | 11-22 |

| 11-16  | Oscillator-Synthesizer A1(S)                                           | 11-24 |

| 11-17  | Divider/Control A1A1(S)                                                | 11-28 |

| 11-18  | RF Generator A1A2(S)                                                   | 11-32 |

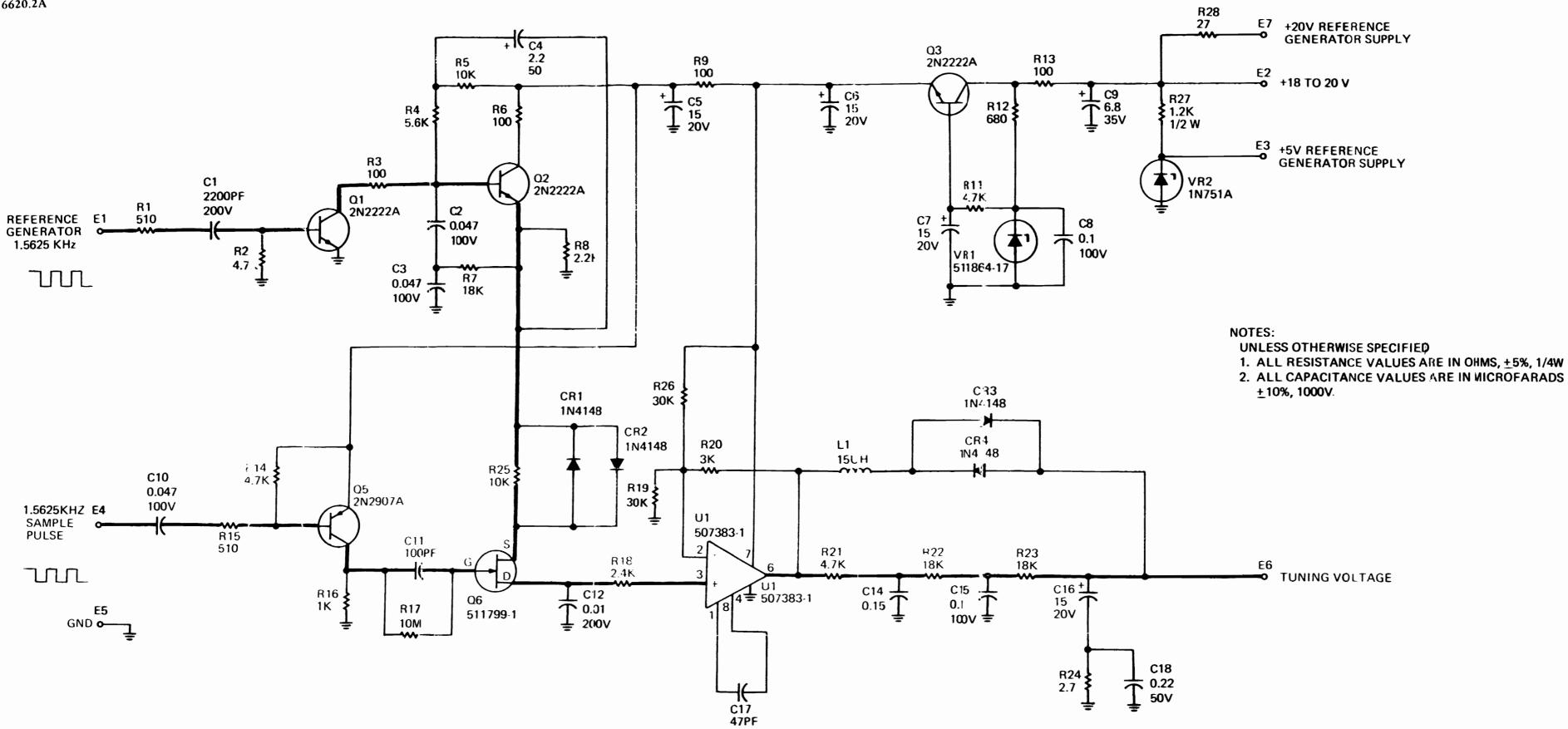

| 11-19  | Phase Comparator A1A3(S)                                               | 11-36 |

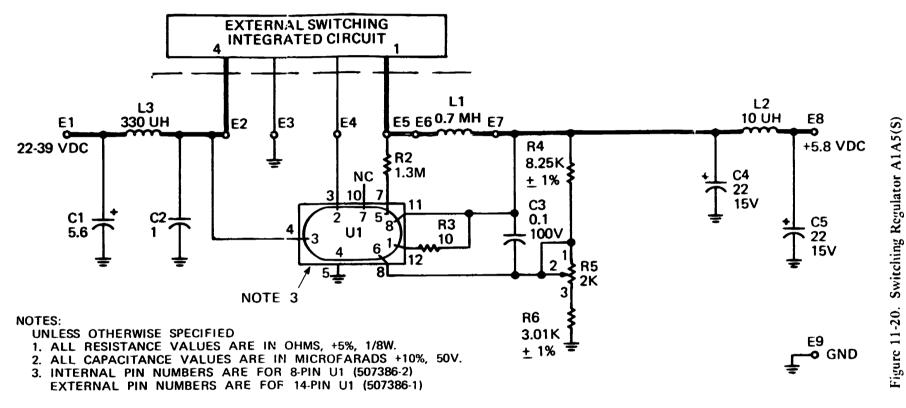

| 11-20  | Switching Regulator A1A5(S)                                            | 11-38 |

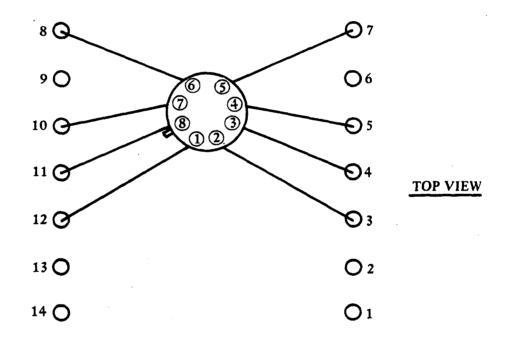

| 11-20A | T0-5/T0-99 Installation on 14-Pin Dual Inline Package (DIP) Socket.    | 11-39 |

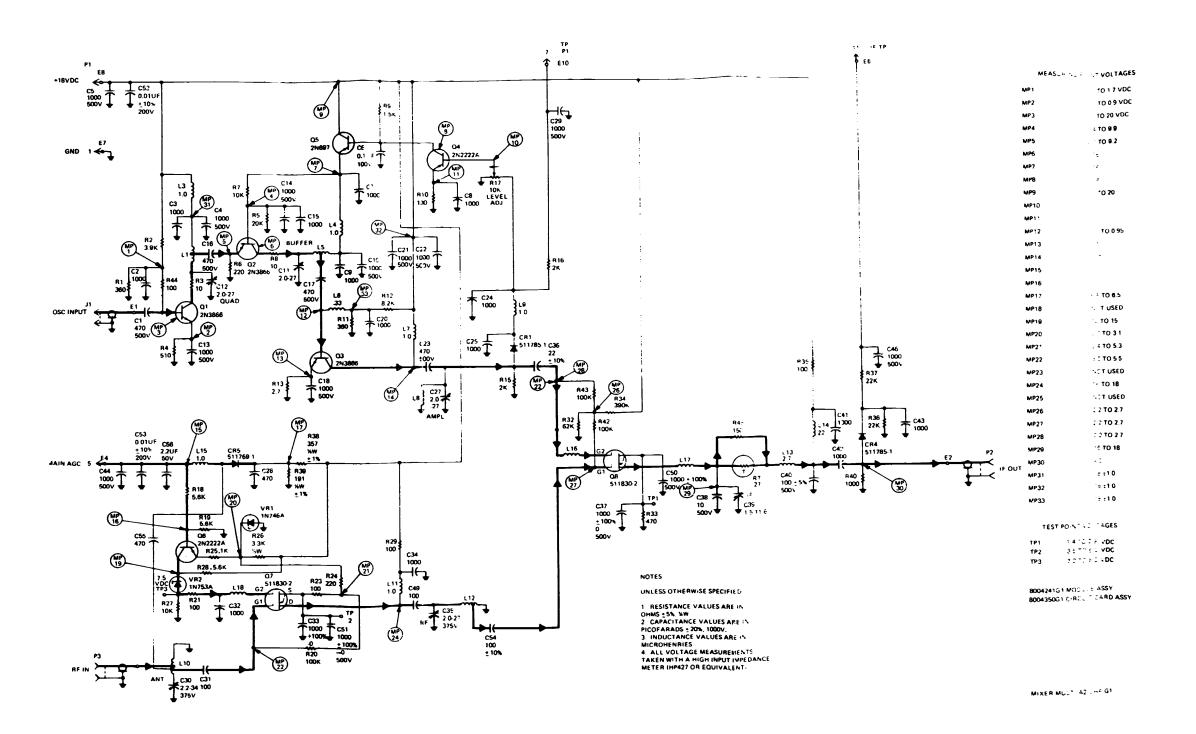

| 11-21  | Mixer/Multiplier (UHF) A2 G1                                           | 11-42 |

| 11-22  | Mixer/Multiplier (UHF) A2 G2                                           | 11-46 |

| 11-23  | Mixer/Multiplier (VHF) A2 G1                                           | 11-50 |

| 11-24  |                                                                        | 11-54 |

| 11-25  | Preamplifier, AF/AGC-Squelch A3                                        | 11-58 |

| 11-26  | Audio Frequency Amplifier A4                                           | 11-62 |

| 11-27  | Buffer Amplifier A5                                                    | 11-64 |

# LIST OF ILLUSTRATIONS (con.)

Page

# <u>Figure</u>

| 11-28 | Electrical Noise Limiter A5                            | 11-68 |

|-------|--------------------------------------------------------|-------|

| 11-29 | IF Amplifier and Detector A6                           | 11-72 |

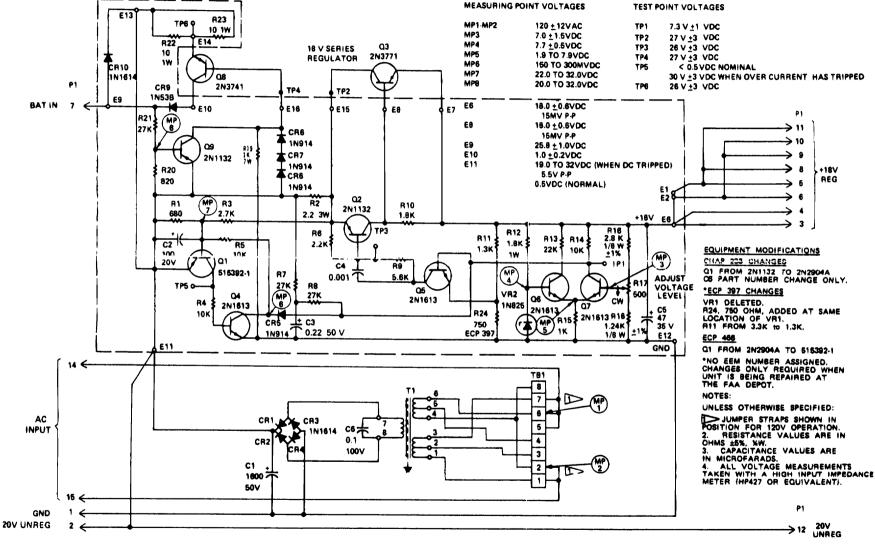

| 11-30 | Power Supply PS1                                       | 11-74 |

| 11-31 | VHF Receiver Functional Blocked Diagram                |       |

| 11-32 | VHF Receiver Functional Blocked Diagram Text           |       |

| 11-33 | UHF Receiver Functional Blocked Diagram                |       |

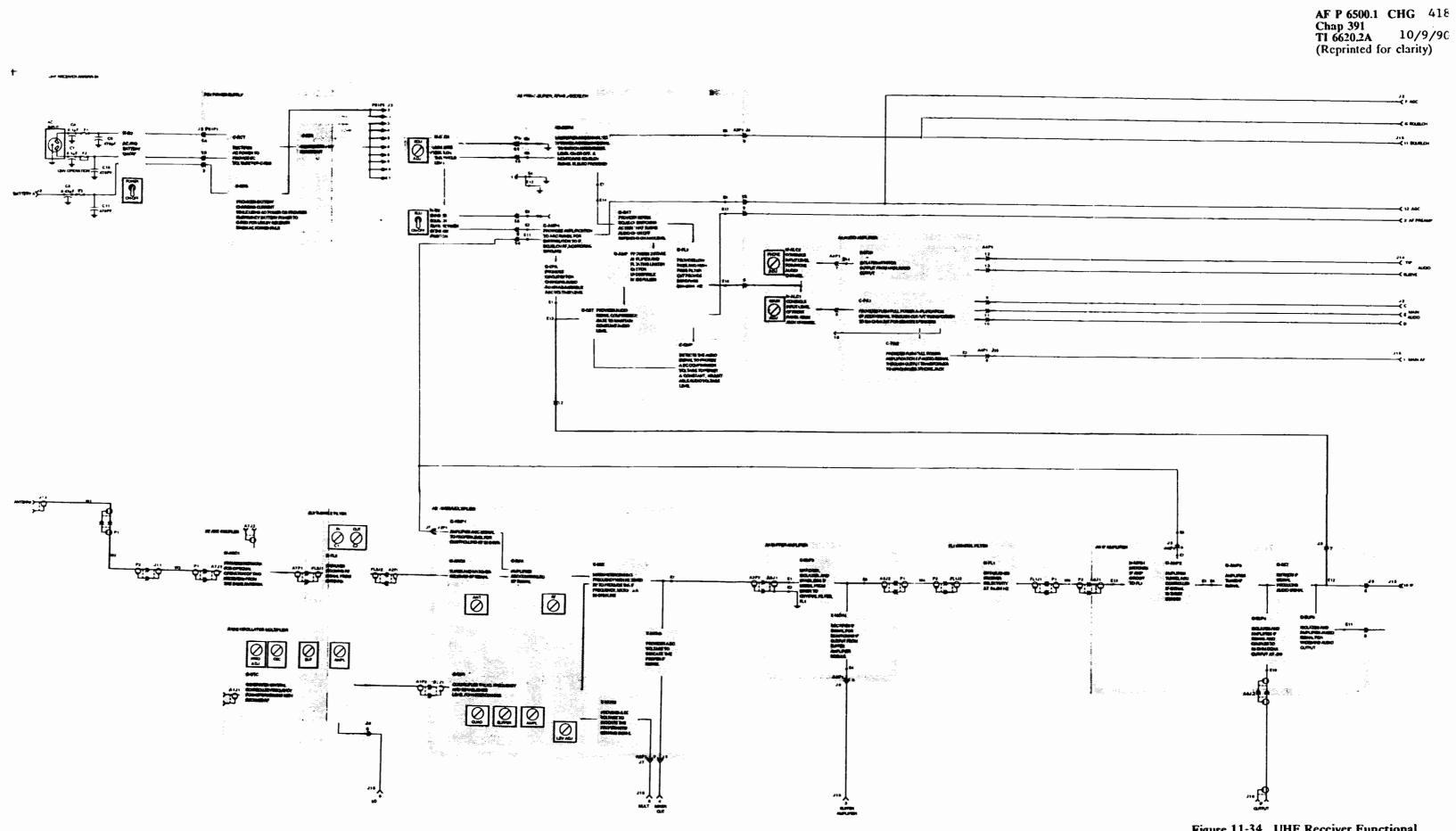

| 11-34 | UHF Receiver Functional Blocked Diagram Text           |       |

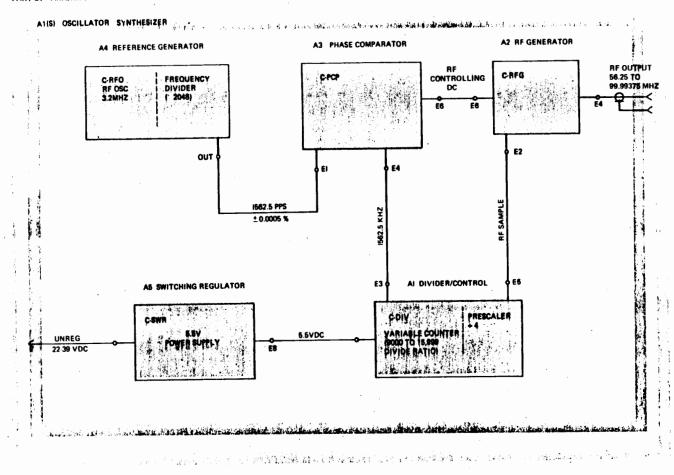

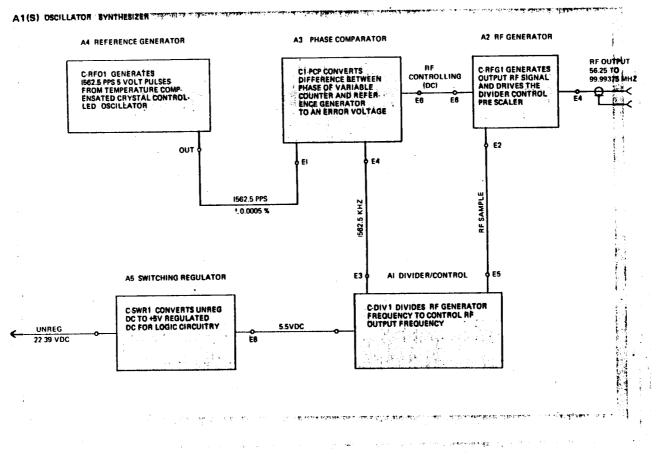

| 11-35 | Oscillator-Synthesizer Functional Blocked Diagram      |       |

| 11-36 | Oscillator-Synthesizer Functional Blocked Diagram Text |       |

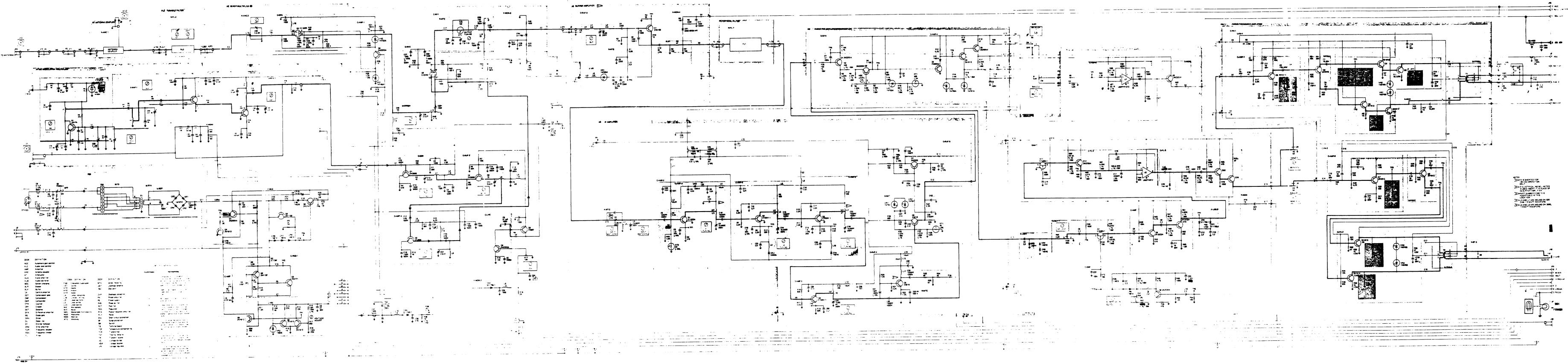

| 11-37 | VHF Receiver Blocked Schematic Diagram                 |       |

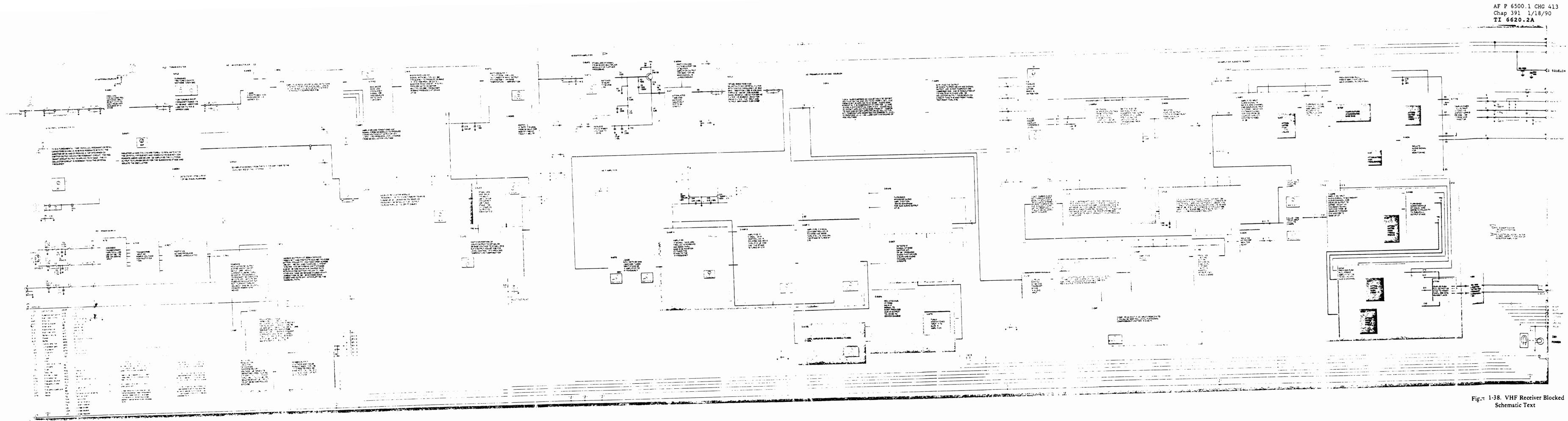

| 11-38 | VHF Receiver Blocked Schematic Text.                   |       |

| 11-39 | UHF Receiver Blocked Schematic Diagram                 |       |

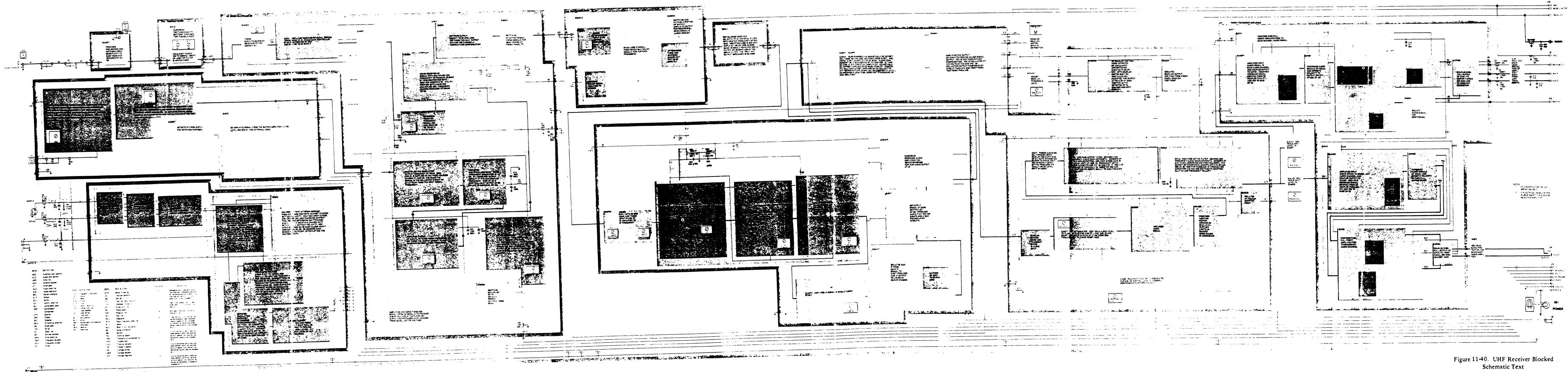

| 11-40 | UHF Receiver Blocked Schematic Text.                   |       |

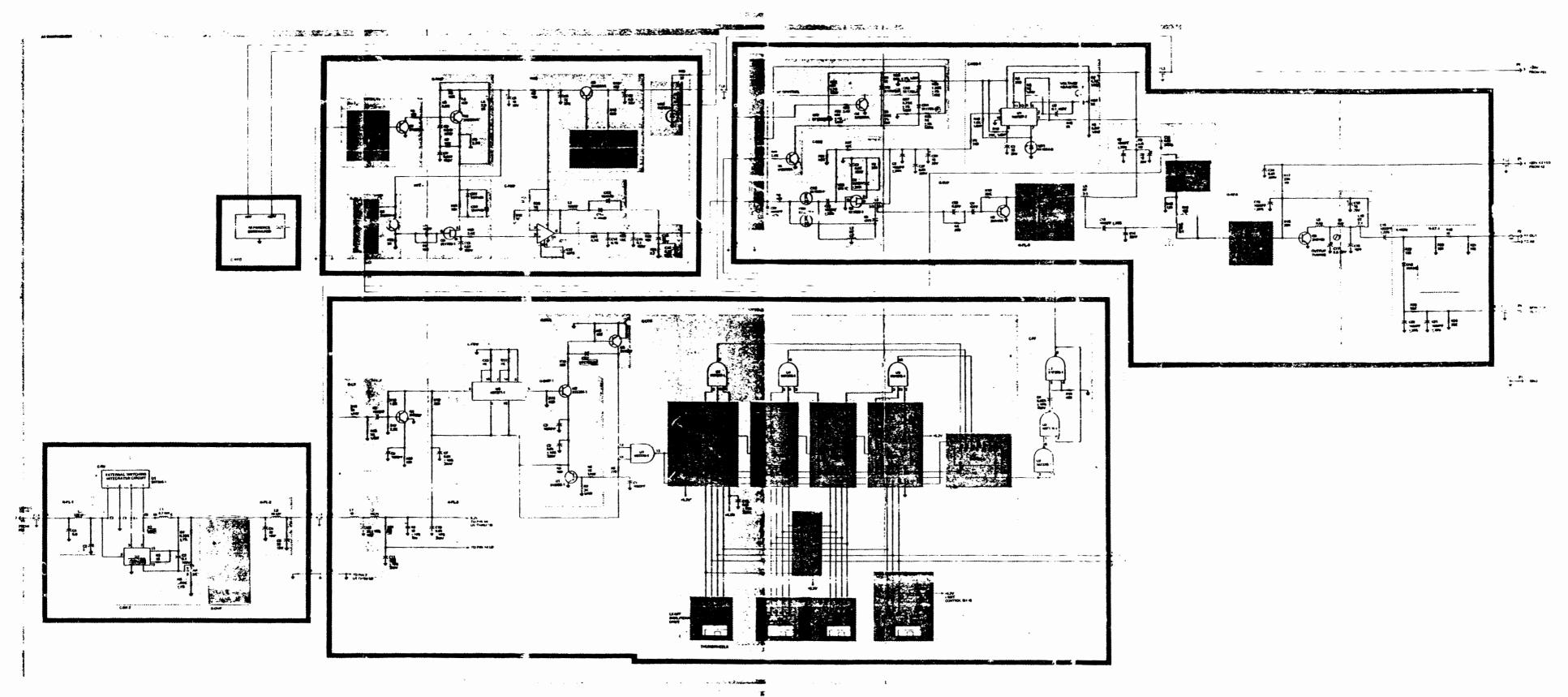

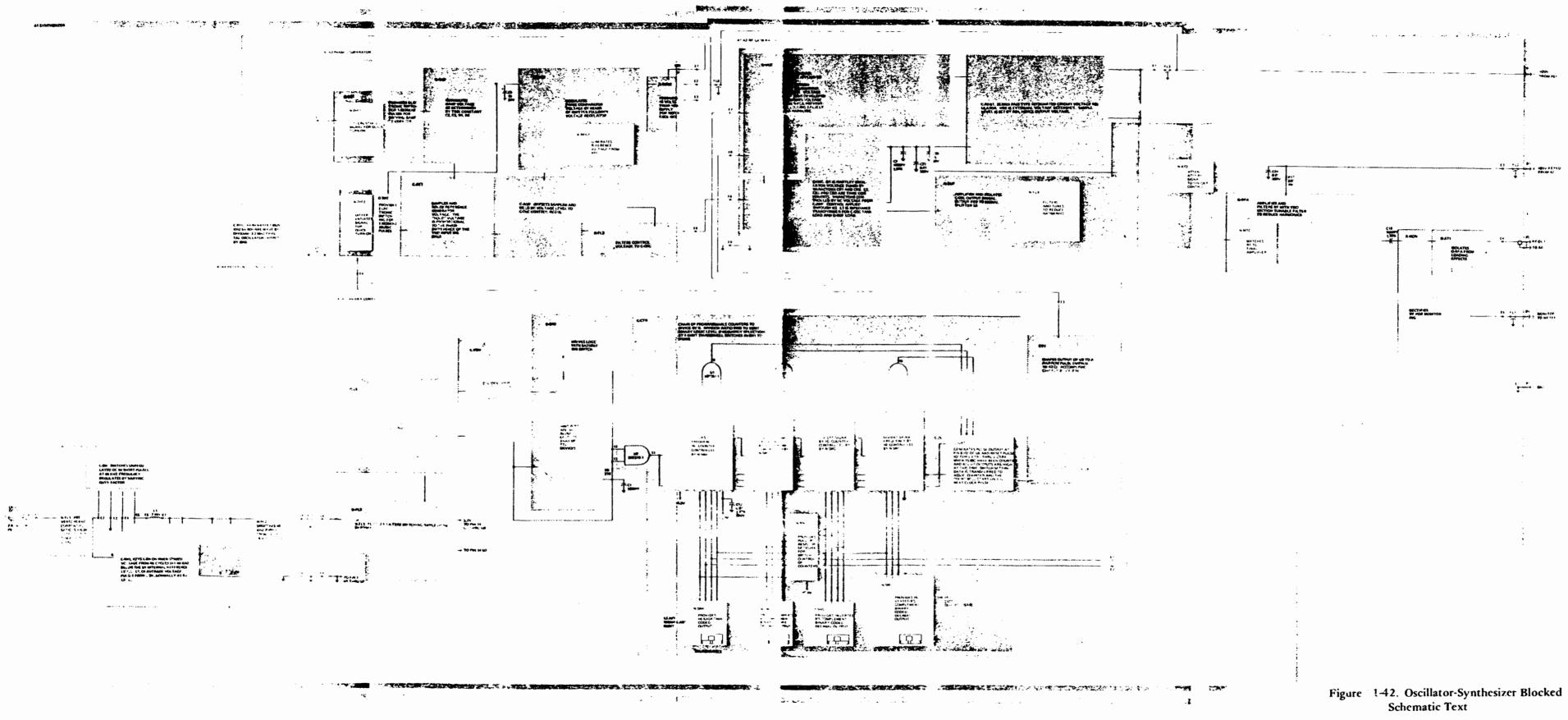

| 11-41 | Oscillator-Synthesizer Blocked Schematic Diagram       |       |

| 11-42 | Oscillator-Synthesizer Blocked Schematic Text          |       |

|       |                                                        |       |

# LIST OF TABLES

| <u>Table</u> |                    | Page |

|--------------|--------------------|------|

| 11-1         | Receiver Wire List | 11-2 |

# AF P 6500.1 CHG 361 Chap 356 1/28/83 FUNCTIONAL INDEX

| Item<br>Desig.                                     | Item Name                         | General<br>Theory<br>Page No. | Detailed<br>Theory<br>Page No. | Schematic<br>Page No. |

|----------------------------------------------------|-----------------------------------|-------------------------------|--------------------------------|-----------------------|

| 1                                                  | Receiver, Radio, UHF, AN/GRR-24   | 11-83                         | 11-95                          | 11-94                 |

| 2                                                  | Receiver, Radio, VHF, AN/GRR-23   | 11-79                         | 11-91                          | 11-90                 |

| 1A1 or 2A1<br>(Deleted)<br>1A1 or 2A1<br>(Deleted) |                                   |                               |                                |                       |

| 1A1(M) or 2A1(M)                                   | Oscillator-Multiplier (8009546G1) |                               | 11-23                          | 11-22                 |

| 1A1(S) or 2A1(S)                                   | Oscillator-Synthesizer            | 11-87                         | 11-99                          | 11-22                 |

| 1A2                                                | Mixer-Multiplier (UHF)            |                               | 11-43                          | 11-42                 |

| 2A2                                                | Mixer-Multiplier (VHF)            |                               | 11-51                          | 11-50                 |

| 1A3 or 2A3                                         | Preamplifier, AF/AGC-Squelch      |                               | 11-59                          | 11-58                 |

| 1A4 or 2A4                                         | Audio Amplifier                   |                               | 11-63                          | 11-62                 |

| 1A5 or 2A5                                         | Buffer Amplifier                  |                               | 11-65                          | 11-64                 |

| 1A5 or 2A5                                         | Electrical Noise Limiter          |                               | 11-69                          | 11-68                 |

| 1A6 or 2A6                                         | IF Amplifier and Detector         |                               | 11-73                          | 11-72                 |

| 1PS1 or 2PS1                                       | Power Supply                      |                               | 11-75                          | 11-74                 |

# AF P 6500.1 CHG 361 Chap 356 1/28/83

-

\*

.

#### CIRCUIT IDENTIFIER CODES

| CATEGO | RY DEFINITIO                                                                                                                                         | N                                            | CATEGORY                          | DE                                                                                                                                                          | FINITION                                                                                             |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

| C      | Composite circuit (one<br>functionalized); compose<br>entities containing one of<br>functional entities (N, C<br>given in this list are prec         | site function<br>for more of<br>(), V, or X) | onal<br>the                       | Q Circuits containing one or more<br>linear elements which may be e<br>active or passive; functional en<br>containing transistors are prece<br>by Q.        |                                                                                                      |  |  |

| L      | Used in logic diagrams of lowest level of functional logic circuits.                                                                                 |                                              |                                   | Circuits containing one or more non<br>linear elements which may be either<br>active or passive; functional entities<br>containing vacuum tubes are precede |                                                                                                      |  |  |

| М      | Microwave components attenuators, etc.).                                                                                                             | (duplexers                                   | S, .                              | by V.                                                                                                                                                       |                                                                                                      |  |  |

| N      | Linear networks; function<br>containing several linear<br>(resistors, capacitors, etc<br>a network or containing<br>element used as network<br>by N. | componer<br>c.) arrange<br>a single          | nts<br>d in                       | linear elements<br>active or passiv                                                                                                                         | ining one or more non-<br>s which may be either<br>ve; functional entities<br>niconductor diodes are |  |  |

| CODE   | DEFINITION                                                                                                                                           | CODE                                         | DEFINITION                        | CODE                                                                                                                                                        | DEFINITION                                                                                           |  |  |

| AGC    | Automatic gain control                                                                                                                               | FQD                                          | Frequency quadrupler              | ТВ                                                                                                                                                          | Terminal board                                                                                       |  |  |

| ALC    | Audio level control                                                                                                                                  | GAT                                          | Gating                            | TFR                                                                                                                                                         | Transformer                                                                                          |  |  |

| AMP    | Amplifier                                                                                                                                            | HTR                                          | Heater                            | TR                                                                                                                                                          | Transmit-receive                                                                                     |  |  |

| ANC    | Antenna coupler                                                                                                                                      | LA                                           | Lamp (indicating)                 | VD                                                                                                                                                          | Voltage divider                                                                                      |  |  |

| AT     | Attenuator                                                                                                                                           | LIM                                          | Limiter, limiting                 | VDR                                                                                                                                                         | Voltage doubler                                                                                      |  |  |

| AUA    | Audio amplifier                                                                                                                                      | LO                                           | Local oscillator                  | VR                                                                                                                                                          | Voltage regulator                                                                                    |  |  |

| AUO    | Audio oscillator                                                                                                                                     | LS                                           | Level shifter                     |                                                                                                                                                             |                                                                                                      |  |  |

| BCG    | Battery charging                                                                                                                                     | LVC                                          | Level control circuit             |                                                                                                                                                             |                                                                                                      |  |  |

| BUF    | Buffer                                                                                                                                               | MIC                                          | Microphone                        |                                                                                                                                                             |                                                                                                      |  |  |

| CA     | Control amplifier                                                                                                                                    | MIX                                          | Mixer                             |                                                                                                                                                             |                                                                                                      |  |  |

| CGT    | Compression gate                                                                                                                                     | MMV                                          | Monostable multivibrator          | г                                                                                                                                                           |                                                                                                      |  |  |

| CMP    | Compression                                                                                                                                          | MOD                                          | Modulator                         |                                                                                                                                                             |                                                                                                      |  |  |

| CMR    | Comparator                                                                                                                                           | MON                                          | Monitor                           |                                                                                                                                                             |                                                                                                      |  |  |

| CTR    | Counter                                                                                                                                              | MTC                                          | Matches                           |                                                                                                                                                             |                                                                                                      |  |  |

| CPR    | Clipper                                                                                                                                              | MTG<br>OSC                                   | Matching                          |                                                                                                                                                             |                                                                                                      |  |  |

| DET    | Detector                                                                                                                                             | USC                                          | Oscillator                        |                                                                                                                                                             |                                                                                                      |  |  |

| DFA    | Differential amplifier                                                                                                                               | PS                                           | Pouros au-alu                     |                                                                                                                                                             |                                                                                                      |  |  |

| DG     | Diode gate                                                                                                                                           | RCT                                          | Power supply<br>Rectifier         |                                                                                                                                                             |                                                                                                      |  |  |

| DL     | Delay line                                                                                                                                           | REG                                          | Regulator                         |                                                                                                                                                             |                                                                                                      |  |  |

| EF     | Emitter follower                                                                                                                                     | RFA                                          | -                                 | -                                                                                                                                                           |                                                                                                      |  |  |

| FDR    | Frequency doubler                                                                                                                                    | RLY                                          | Radio frequency amplifie<br>Relay | Γ.                                                                                                                                                          |                                                                                                      |  |  |

| FDV    | Frequency divider                                                                                                                                    | SW                                           | Switch                            |                                                                                                                                                             |                                                                                                      |  |  |

| FL     | Filter                                                                                                                                               | 11                                           | Switch                            |                                                                                                                                                             |                                                                                                      |  |  |

.

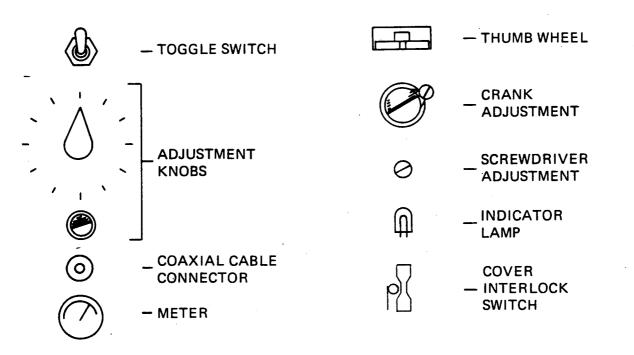

#### **EXPLANATION OF SPECIAL SYMBOLS**

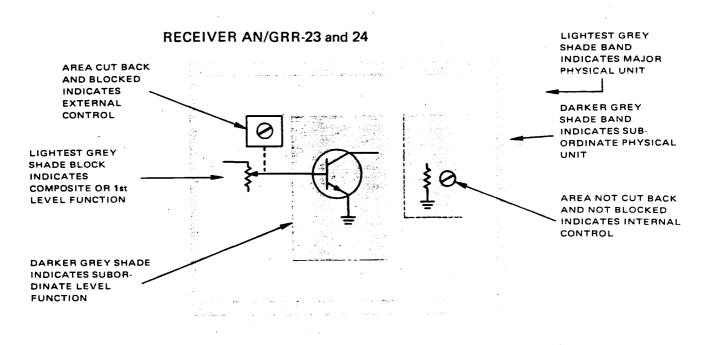

### **EXPLANATION OF SHADED AREAS**

#### SECTION 11

#### DIAGRAMS

<u>11.1 INTRODUCTION</u>.- This section contains the schematic diagrams for the vhf and uhf receivers and their subassemblies. The schematics of the individual integrated circuits used in the receiver are also included. Shaded blocked diagrams and texts and blocked schematic diagrams and texts complete this section. The interconnecting wiring between subassemblies and between subassemblies and external connections is listed in table 11-1.

11.2 USE OF SUBASSEMBLY SCHEMATIC DIAGRAMS.- The subassembly schematics in this section are intended chiefly as maintenance tools together with the assembly drawings and photographs in section 10. Test points (TP) and measurement points (MP) are accentuated and the d.c. voltages at these points are listed on each schematic.

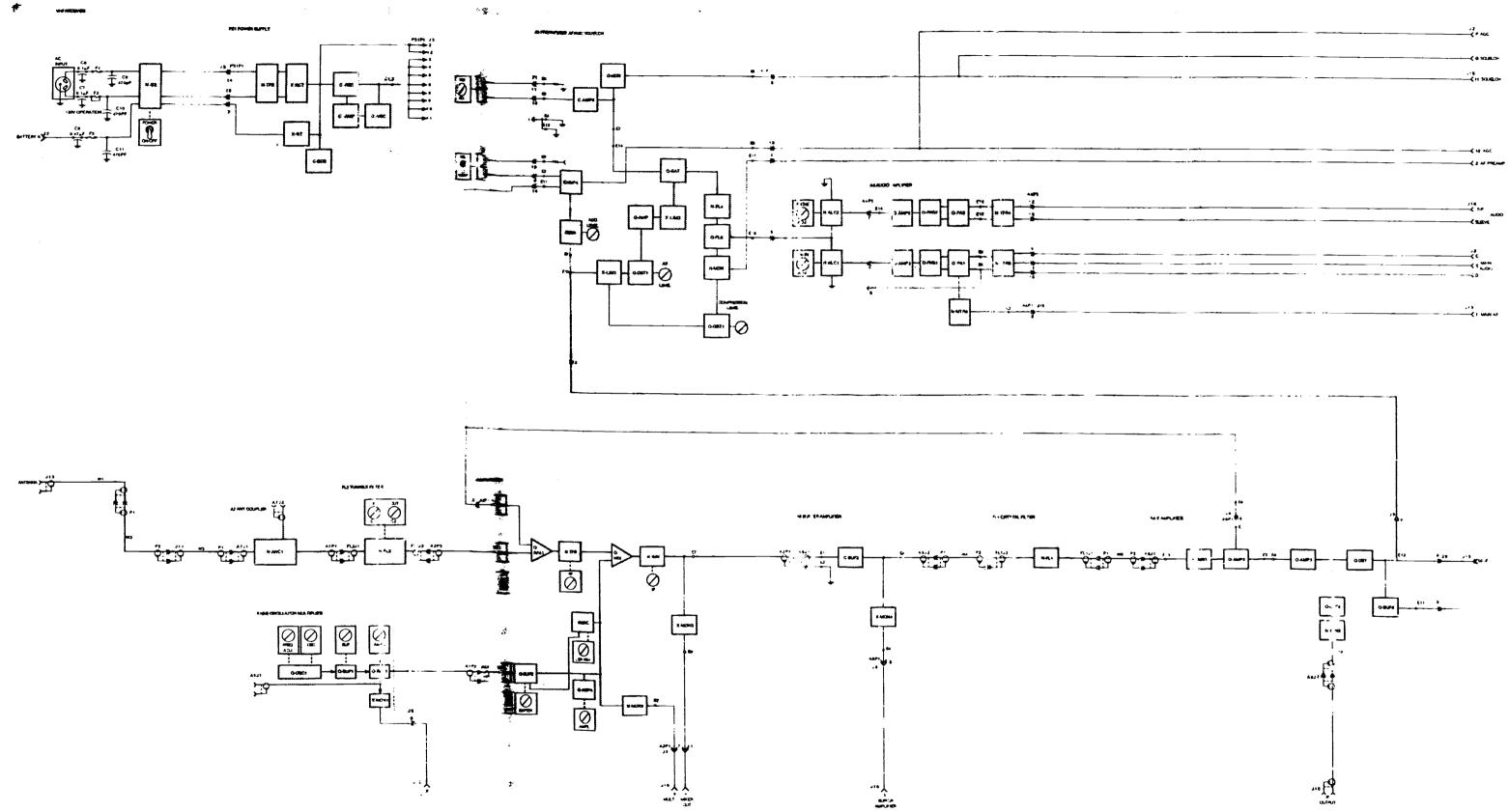

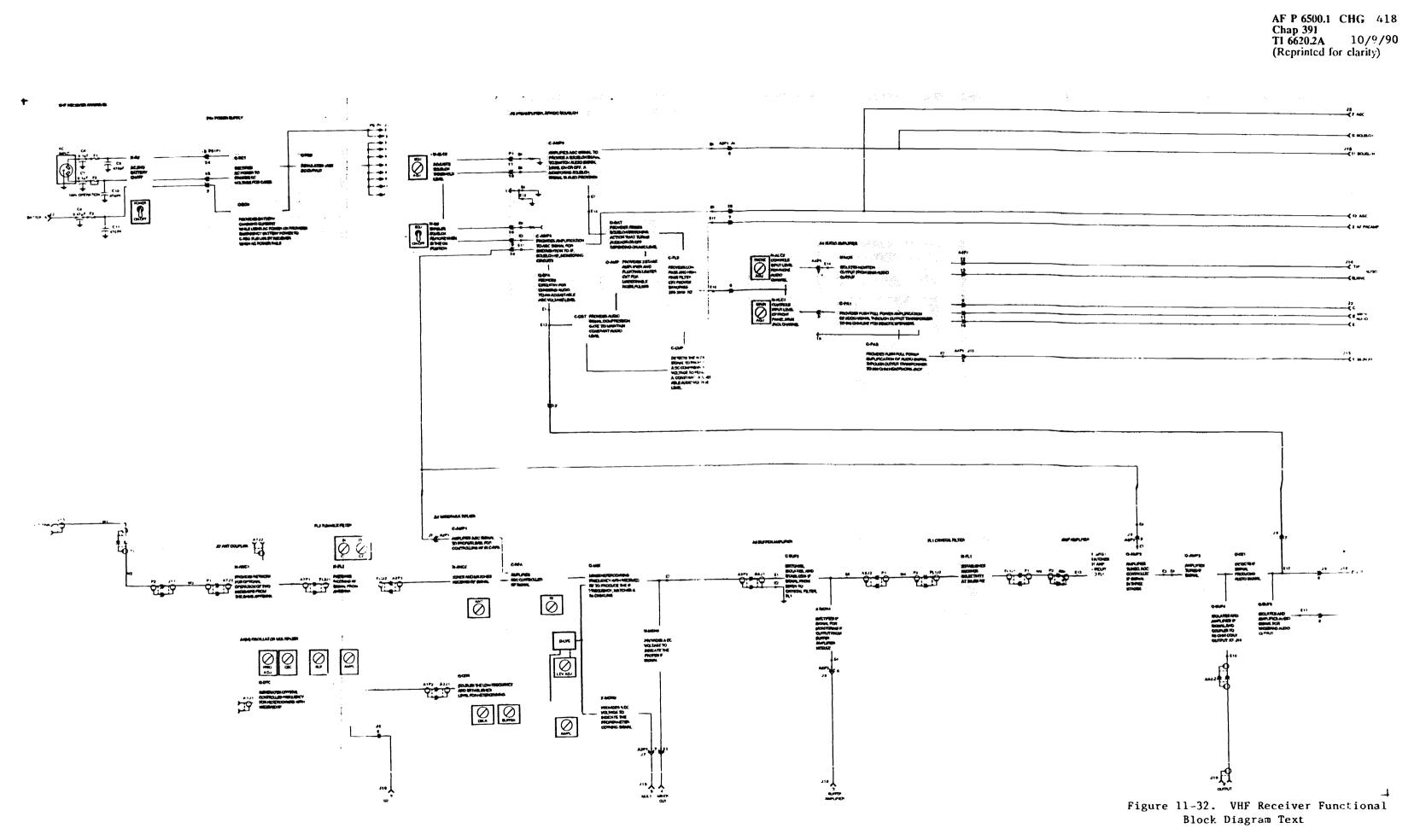

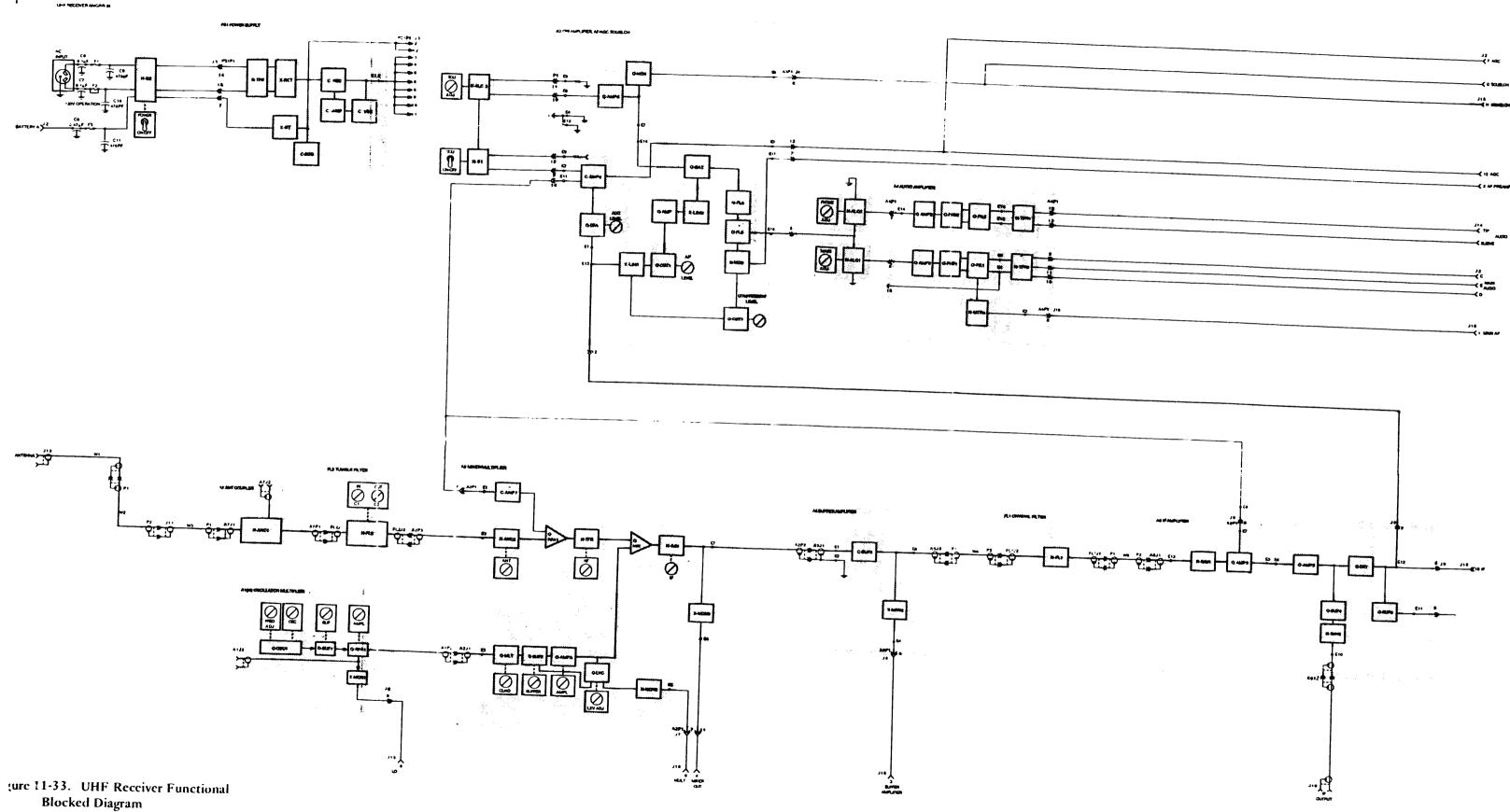

<u>11.3 SHADED BLOCKED DIAGRAMS AND TEXTS</u>. Figures 11-30 through 11-33 present a secondlevel functional description of the vhf and uhf receivers in blocked diagrams and companion blocked texts. Figures 11-34 and 11-35 present a functional block diagram and companion text for the optional oscillator-synthesizer module that may be used in either receiver unit.

<u>11.4 SHADED BLOCKED SCHEMATIC DIAGRAMS AND TEXTS</u>. Figures 11-36 through 11-39 present the shaded functionally oriented blocked schematic diagrams and companion text discussions of the uhf and vhf receivers, respectively. It should be noted in these schematics that the mixer/multiplier (A2) is shown only in the G2 configuration, which is only slightly different from the G1 configuration. Figures 11-40 and 11-41 present the shaded functionally oriented blocked schematic dia-

gram and companion text of the oscillator-multiplier and the optional oscillator-synthesizer module that may be used in either receiver unit.

# Table 11-1. Receiver Wire List

|                | From      | n termina | 1           | То         | terminal |             |      |       |       | Approx.            |       |         |

|----------------|-----------|-----------|-------------|------------|----------|-------------|------|-------|-------|--------------------|-------|---------|

| Wire<br>number | Connector | Pin       | Conn<br>Iug | Connector  | Pin      | Conn<br>lug | Туре | Gauge | Color | length<br>(inches) | Notes | Remarks |

|                |           |           |             |            |          | 8           | -77- |       |       |                    |       |         |

| 1              | J15       | 16        | 2           | E4         |          | · <b>4</b>  | E    | 22    | - 0   | 9                  |       |         |

| 2              | J15       | 14        | 2           | J3         | 2        | DF          | E    | 22    | 7     | 115                |       |         |

| 3              | J15       | 13        | 2           | J3         | 3        | DF          | E    | 22    | 2     | 11¾                |       |         |

| 4              | J15       | 12        | 2           | J4         | 13       | DF          | Е    | 22    | 4     | 13½                |       |         |

| 5              | J15       | 11        | 2           | J4         | 8        | DF          | Ε    | 22    | 9     | 13¾                |       |         |

| 6              | J15       | 10        | 2           | J9         | 8        | DF          | Y    | 22    | 5     | 15%                | 1     |         |

| 7              | J15       | 9         | 2           | J6         | 5        | DF          | E    | 22    | 6     | 15%                |       |         |

| 8              | J15       | 8         | 2           | J7         | 7        | DF          | Е    | 22    | 95    | 13                 |       |         |

| 9              | J15       | 6         | 2           | J6         | 6        | DF          | Е    | 22    | 1     | 16¼                |       |         |

| 10             | J15       | 4         | 2           | <b>J</b> 7 | 11       | DF          | Е    | 22    | 96    | 13¾                |       |         |

| 11             | J15       | 3         | 2           | J8         | 5        | DF          | Е    | 22    | 93    | 16                 |       |         |

| 12             | J15       | 2         | 2           | J4         | 7        | DF          | E    | 22    | 90    | 16                 |       |         |

| 13             | J15       | 1         | 2           | J5         | 8        | DF          | E    | 22    | · 8   | 185                |       |         |

| 14             | J14       | Т         | 4           | J5         | 13       | DF          | Е    | 22    | 96    | 16½                |       |         |

| 15             | J14       | R         | 4           | J5         | 12       | DF          | Е    | 22    | 95    | 16%                |       |         |

| 16             | <b>S1</b> | 1         | 4           | · J4       | 15       | DF          | Е    | 22    | 91    | 5                  |       |         |

| 17             | <b>S1</b> | 2         | 4           | <b>R1</b>  | 1        | 2           | E    | 22    | 9     | 4                  |       |         |

| <b>18</b> ·    | <b>S1</b> | 3         | 4           | J4         | 9        | DF          | E    | 22    | 3     | 15                 |       |         |

| <b>19</b> `    | <b>R1</b> | 2         | 4           | J4         | 10       | DF          | Е    | 22    | 7     | 14½                |       | •       |

| 20             | R1        | 3         | 2           | J4         | 11       | DF          | Е    | 22    | 8     | 14½                |       |         |

| 21             | R3        | 1         | 2           | R2         | 1        | 2           | E    | 22    | 1     | 4                  |       |         |

| 22             | R3        | 1         | 2           | J4         | 5        | DF          | Ε    | 22    | 1     | 15                 |       |         |

| 23             | R3        | 3         | 2           | R2         | 3        | 2           | E    | 20    | 0     | 4                  |       |         |

| 24             | R3        | 3         | 2           | E4         |          | 4           | Е    | 20    | 0     | 10¾                |       |         |

| 25             | R3        | 2         | 2           | ]5         | 7        | DF          | Е    | 22    | 7     | 17                 |       |         |

| 26             | R2        | 2         | 2           | J5         | 5        | DF          | E    | 22    | 90    | 16¾                |       |         |

| 27             | J3        | 1         | DF          | E3         |          | 4           | Е    | 20    | 0     | 4¼                 |       |         |

| 28             | J3        | 4         | DF          | J6         | 3        | DF          | Е    | 22    | 2     | 9                  |       |         |

| 29             | J3        | 6         | DF          | J7         | 3        | DF          | Е    | 22    | 2     | 6½                 |       |         |

| 30             | J3        | 8         | DF          | <b>J</b> 8 | 3        | DF          | E    | 20    | 2     | 81/2               |       |         |

| 31             | J3        | 9         | DF          | J9         | 3        | DF          | E    | 20    | 2     | 9                  |       |         |

TI 6620.2A

| Wire   |              | ı termin | Conn       |            | terminal | Conn      |      |       |       | Approx.<br>length | Υ.    |         |          |

|--------|--------------|----------|------------|------------|----------|-----------|------|-------|-------|-------------------|-------|---------|----------|

| number | Connector    | Pin      | lug        | Connector  | Pin      | lug       | Туре | Gauge | Color | (inches)          | Notes | Remarks |          |

| 32     | J3           | 10       | DF         | J4         | 3        | DF        | E    | 20    | 2     | 81⁄2              |       |         |          |

| 33     | J3           | 11       | DF         | J5         | 3        | DF        | E    | 20    | 2     | 10                |       |         |          |

| 34     | ]3           | 12       | DF         | J6         | 2        | DF        | E    | 22    | 7     | 8¾                |       |         |          |

| 35     | J4           | 1        | DF         | E3         |          | 4         | Е    | 20    | 0     | 4                 |       |         |          |

| 37     | J4           | 6        | DF         | J5         | 15       | DF        | E    | 22    | 6     | 8¾                |       |         |          |

| 38     | J4           | 14       | DF         | E6         |          | 2         | E    | 22    | 5     | 6                 |       |         |          |

| 39     | J5           | 1        | DF         | E2         |          | 4         | E    | 20    | 0     | 4¼                |       |         |          |

| 40     | J5           | 9        | DF         | C2         | 1        | 25        | E    | 22    | 4     | 11¼               | 2     |         |          |

| 41     | J5           | 11       | DF         | · C3       | 1        | <b>2S</b> | E    | 22    | 3     | 11¼               | 2     |         |          |

| 42     | J5           | 10       | DF         | C4         | 1        | <b>2S</b> | Ε    | 22    | 9     | 11¼               | 2     |         |          |

| 43     | J7           | 1        | ÐF         | E7         |          | 4         | E    | 20    | 0     | 71⁄2              |       |         |          |

| 44     | J7           | 5        | DF         | E6         |          | 2         | Е    | 22    | 5     | 4                 |       |         |          |

| 45     | J6           | 1        | DF         | E7         |          | 4         | E    | 20    | 0     | 3                 |       |         |          |

| 46     | J8           | 1        | DF         | E7         |          | 4         | E    | 20    | 0     | 7 1⁄2             |       |         |          |

| 47     | J9           | 9        | DF         | E6         |          | 2         | E    | 22    | 5     | 10                |       |         |          |

| 48     | .s <b>J9</b> | 1        | DF         | E5         |          | 4         | E    | 20    | 0     | 5                 |       |         |          |

| 49     | <b>J</b> 9   | 5        | DF         | C5         |          | <b>2S</b> | Y    | 22    | 6     | 10                | 3&2   |         |          |

| 50     | J9           | 7        | DF         | J4         | 12       | DF        | E    | 22    | 95    | 7 <u>3</u> 4      |       |         |          |

| 53     | C1           | 1        | 28         | E6         |          | 2         | Е    | 22    | 5     | 14                | 2     |         |          |

| 54     | <b>C8</b>    | 1        | <b>2S</b>  | XF3        | 1        | 4         | Е    | 22    | 6     | 2334              | 2     |         |          |

| 55     | XF3          | 2        | 4          | <b>S2</b>  | 3        | 4         | E    | 22    | 7     | 91/2              | ÷     |         |          |

| 56     | S2           | 7        | 4          | J3         | 7        | DF        | Е    | 22    | 6     | 18                |       |         |          |

| 60     | J3           | 5        | DF         | J6         | 4        | DF        | E    | 22    | 92    | 7                 |       |         |          |

| 61 -   | C6           | 1        | <b>2</b> S | XF1        | 1        | 4         | R    | 20    | 8     | 221/2             |       |         | , H<br>H |

| 62     | C7           | 1        | 2S         | SF2        | 1        | 4         | R    | 20    | 98    |                   |       |         | σ        |

| 63     | XF1          | 2        | 4          | S2         | 1        | 4         | R    | 20    | 1     | 11                |       |         | 62       |

| 64     | XF2          | 2        | 4          | S2         | 2        | 4         | R    | 20    | 91    |                   |       |         | ö        |

| 65     | Withdraw     | n by A   | F P 6500.  | 1 CHG Chap | , .      |           |      |       |       |                   |       |         | N        |

| 66     | Withdraw     |          |            |            |          |           |      |       |       |                   |       |         | * 🎽      |

| 67     | <b>S2</b>    | 5        | 4          | J3         | 14       | DF        | R    | 20    | 8     | 81/2              |       |         |          |

| 68     | <b>S2</b>    | 6        | 4          | J3         | 15       | DF        | R    | 20    | 98    |                   |       |         |          |

Table 11-1. Receiver Wire List (con.)

.

|   | Table 11-1. Receiver Wire List (con.) |                   |                 |                    |                 |                 |             |        |          |        |                               |       |         |                                    |

|---|---------------------------------------|-------------------|-----------------|--------------------|-----------------|-----------------|-------------|--------|----------|--------|-------------------------------|-------|---------|------------------------------------|

|   | Wire<br>number                        | From<br>Connector | n termin<br>Pin | nal<br>Conn<br>lug | To<br>Connector | terminal<br>Pin | Conn<br>lug | Туре   | Gauge    | Color  | Approx.<br>length<br>(inches) | Notes | Remarks | F 6500.1<br>ap 391 1<br>: 6620.2:  |

| * | 69<br>70                              | E4<br>J15         | 13              | 2<br>2             | XDS1<br>XDS1    | 1<br>2          | 2<br>2      | E<br>E | 22<br>22 | 0<br>2 | 121/2<br>141/2                |       |         | . CHG 413<br>./18/90<br><b>A</b> * |

# **NOTES - CODE IDENTIFICATION**

| "Wire number" colum | n: Numbers 36, 51, 52, 57, 58, and 59 deleted. | "Color" column: | 0 Black                        | 6 Blue                      |  |

|---------------------|------------------------------------------------|-----------------|--------------------------------|-----------------------------|--|

|                     |                                                |                 | 1 Brown                        | 7 Violet                    |  |

| "Conn lug" columns: | DF denotes 502056-402 contact, female          |                 | 2 Red                          | 8 Gray                      |  |

| 2                   | S denotes sleeving, insulation                 |                 | 3 Orange                       | 9 White                     |  |

|                     | 2 denotes 1/4" strip length                    |                 | 4 Yellow                       |                             |  |

|                     | 4 denotes 1/2" strip length                    |                 | 5 Green                        |                             |  |

| "Type" column:E d   | enotes 4590 wire                               | "Notes" column: | 1 Solder shields of wire gates |                             |  |

| `Y d                | enotes 4596 wire, shielded and jacketed        |                 |                                | eeving, insulation          |  |

| R de                | enotes 517875 wire, twisted pair               |                 | 3 Solder shi                   | eld of wire 49 at E1 and E5 |  |

U.S. GOVERNMENT PRINTING OFFICE: 1990-768-016/20104

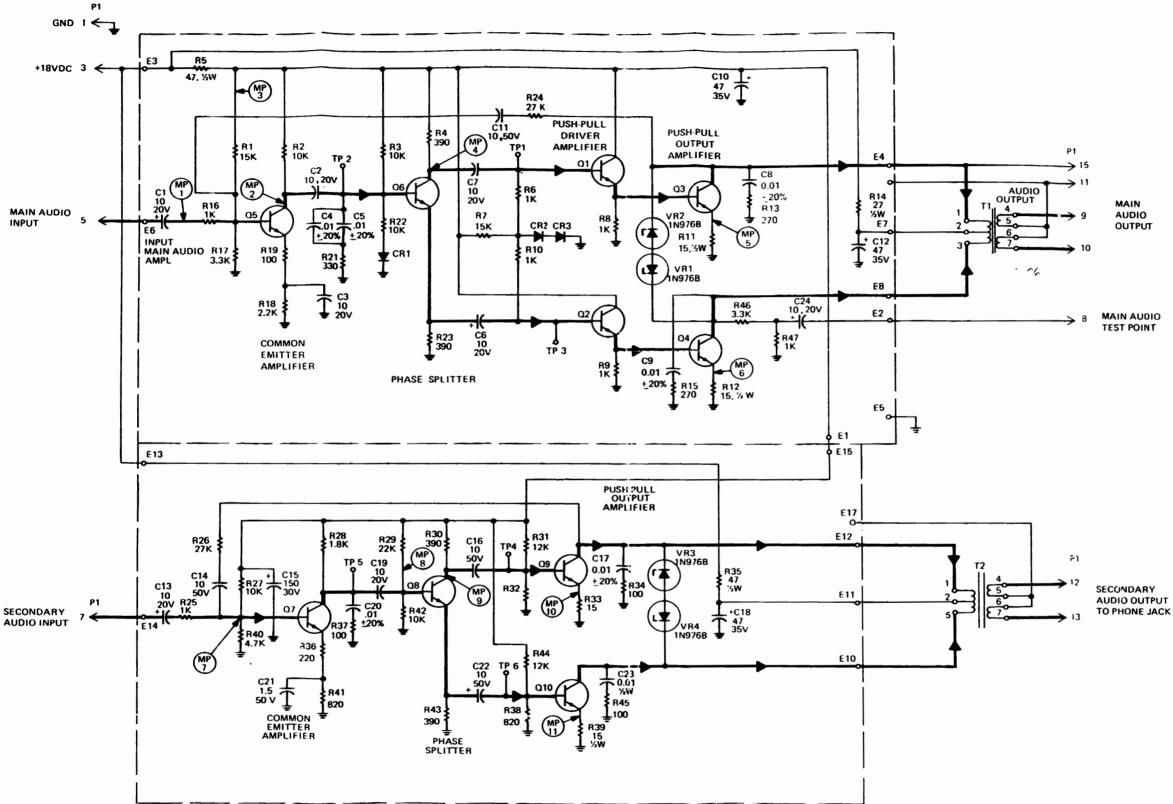

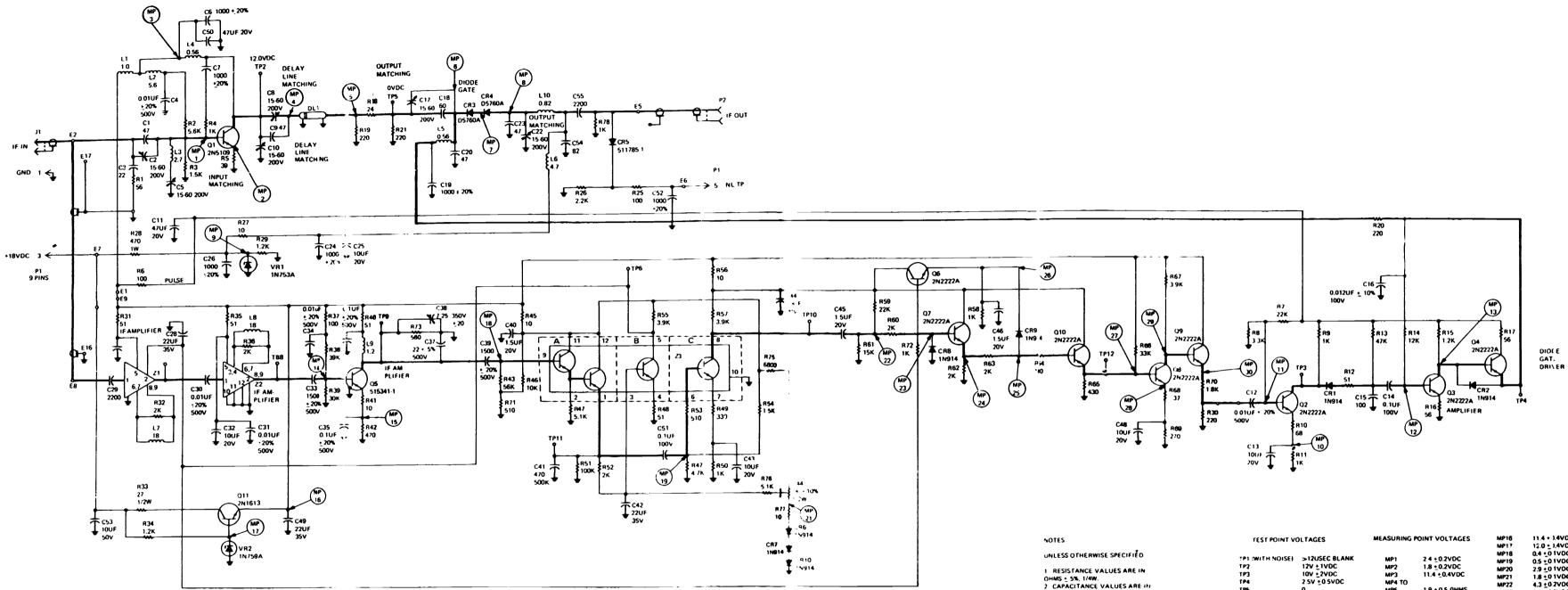

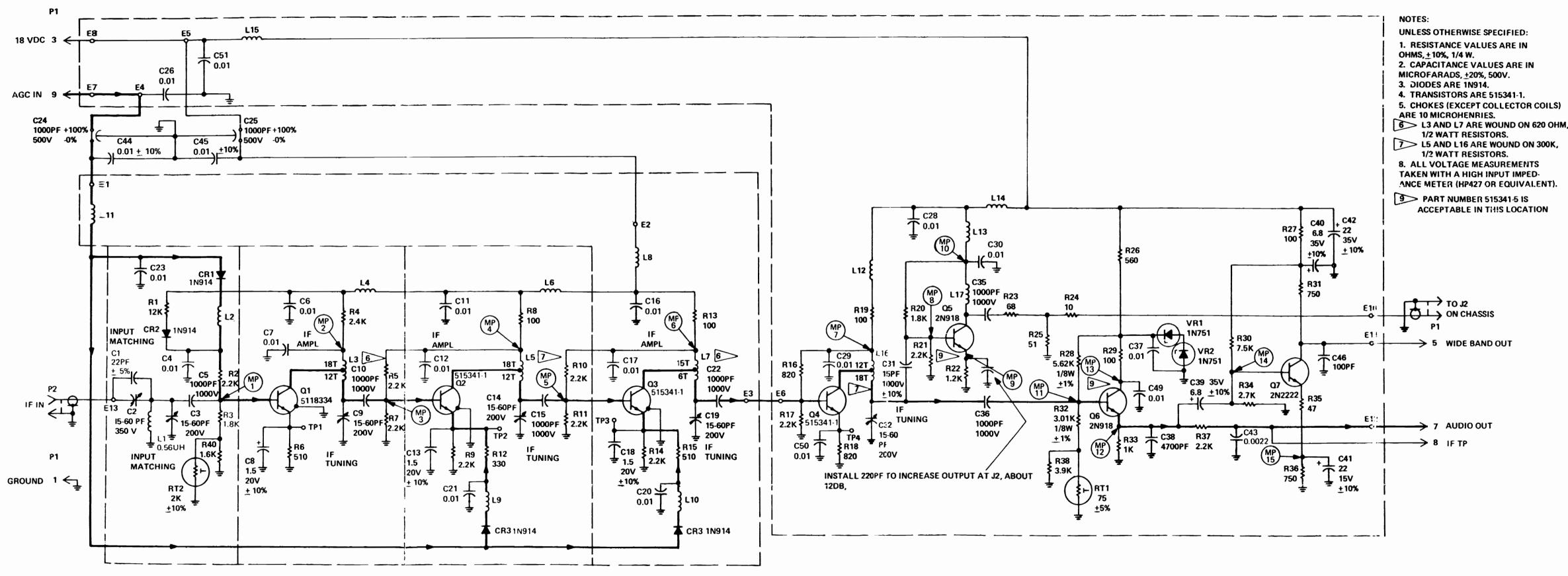

Figure 11-1. VHF/UHF Receiver Schematic

PIN ASSIGNMENT (TOP VIEW)

Figure 11-2. Fixed Resistor Network Integrated Circuit (509435-1)

PIN ASSIGNMENT (TOP VIEW)

#### POSITIVE LOGIC: Y = ABC

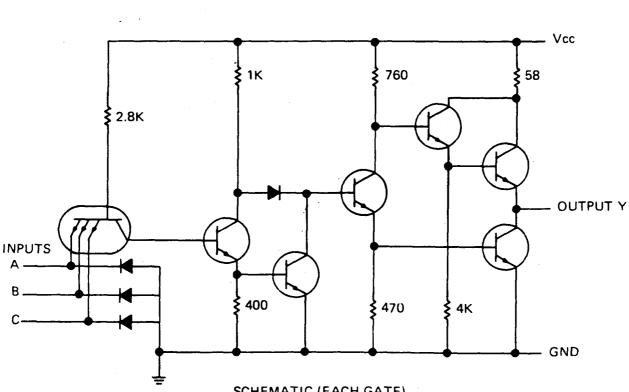

SCHEMATIC (EACH GATE)

PIN ASSIGNMENT (TOP VIEW)

SCHEMATIC (EACH GATE)

Figure 11-5. Operational Amplifier Integrated Circuit (SN52741L-00)

(

Figure 11-6. Operational Amplifier Integrated Circuit (LM101AH)

Figure 11-7. Switching Regulator Integrated Circuit (PIC600)

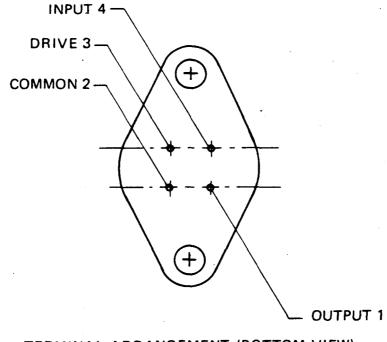

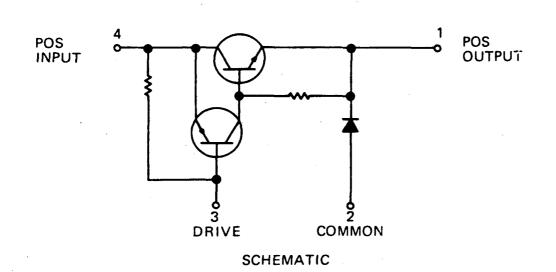

#### **TERMINAL ARRANGEMENT (BOTTOM VIEW)**

Figure 11-8. Transistor Array Integrated Circuit (CA3118T)

(5) Q<sub>A</sub>

.<u>(9)</u> 0<sub>8</sub>

(<u>(2)</u> 0<sub>C</sub>

-<u>(1</u>2)<sub>QD</sub>

Preset

>TOA

Clear

QB

'ск

7

Preset

, a<sub>D</sub>F

CK

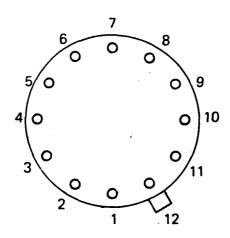

# Figure 11-9. High-Speed Counter Integrated Circuit (SN54196J-00)

| INPUTS |       |       |           |   | OUTPUTS        |    |

|--------|-------|-------|-----------|---|----------------|----|

| PRESET | CLEAR | CLOCK | J         | ĸ | 0              | 0  |

| L      | H     | x     | X         | х | н              | L. |

| н      | L     | X     | X         | Х | L              | н  |

| L      | L     | X     | X         | X | Н.             | Н• |

| н      | Н     | **    | L         | L | 0 <sub>0</sub> | QO |

| н      | Η     | **    | н         | L | н              | L  |

| н      | н     | **    | L         | Н | L              | N  |

| н      | н     |       | H.        | н | TOGG           | LE |

| н      | н     | H.    | X         | X | _ QO           | QO |

|        |       |       | ,,,,,,,,, |   |                |    |

|        |       |       |           |   |                |    |

X = IRRELEVANT

FUNCTION TABLE

\*THIS CONFIGURATION IS NONSTABLE; IT WILL NOT PERSIST WHEN PRESET & CLEAR INPUTS RETURN TO THEIR IN-ACTIVE (HIGH) LEVEL. \*\*TRANSITION FROM HIGH TO LOW LEVEL "TOGGLE" = EACH OUTPUT CHANGES TO THE COMPLEMENT OF ITS PREVIOUS LEVEL ON EACH ACTIVE TRANSITION (PULSE) OF THE CLOCK. "OO" = THE LEVEL OF Q BEFORE THE INDICATED INPUT CONDITIONS WERE ESTABLISHED.

FUNCTIONAL BLOCK DIAGRAM

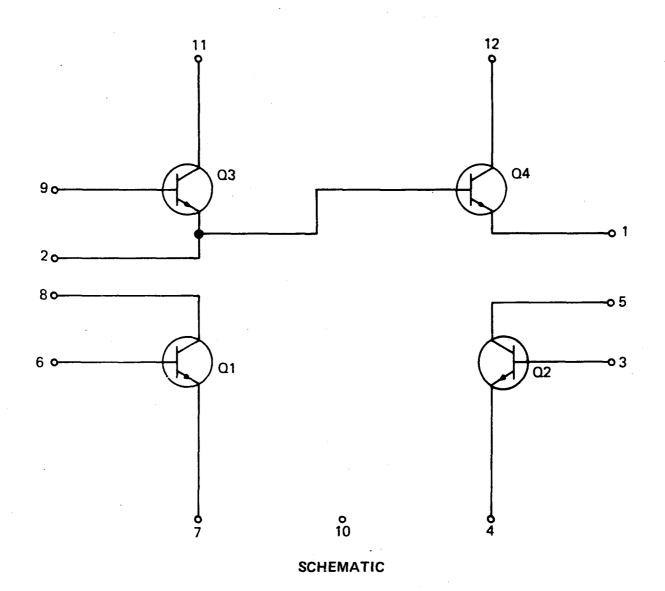

Figure 11-11. Edge-Triggered J-K Flip Flop Integrated Circuit (SN54H102J-00)

A CLOCK H IS A CLOCK TRANSITION FROM A LOW TO A HIGH STATE

CIRCUIT SCHEMATIC 1/2 OF CIRCUIT SHOWN

**RS TRUTH TABLE**

| R                  | S | Qn+1 |  |  |  |  |

|--------------------|---|------|--|--|--|--|

| L                  | L | Qn   |  |  |  |  |

| L                  | Н | н    |  |  |  |  |

| Н                  | L | L    |  |  |  |  |

| н                  | н | N.D. |  |  |  |  |

| N.D. = NOT DEFINED |   |      |  |  |  |  |

CLOCKED TRUTH TABLE  $\begin{array}{c|c}

C & D & Q_{n+1} \\

\hline

L & 0 & Q_n \\

\hline

H & L & L \\

\hline

H & H & H \\

\hline

0 = DON'T CARE \\

C = C_E + C_C

\end{array}$

Figure 11-12. Dual Master-Slave (D-Type) Flip Flop Integrated Circuit (MC10531L)

- Vcc1

~ v<sub>EE</sub>

AF P 6500.1 CHG 361 Chap 356 1/28/83

Figure 11-13. Crystal Oscillator A1 G1 (This figure deleted)

Figure 11-14. Crystal Oscillator A1 G2 (This figure deleted)

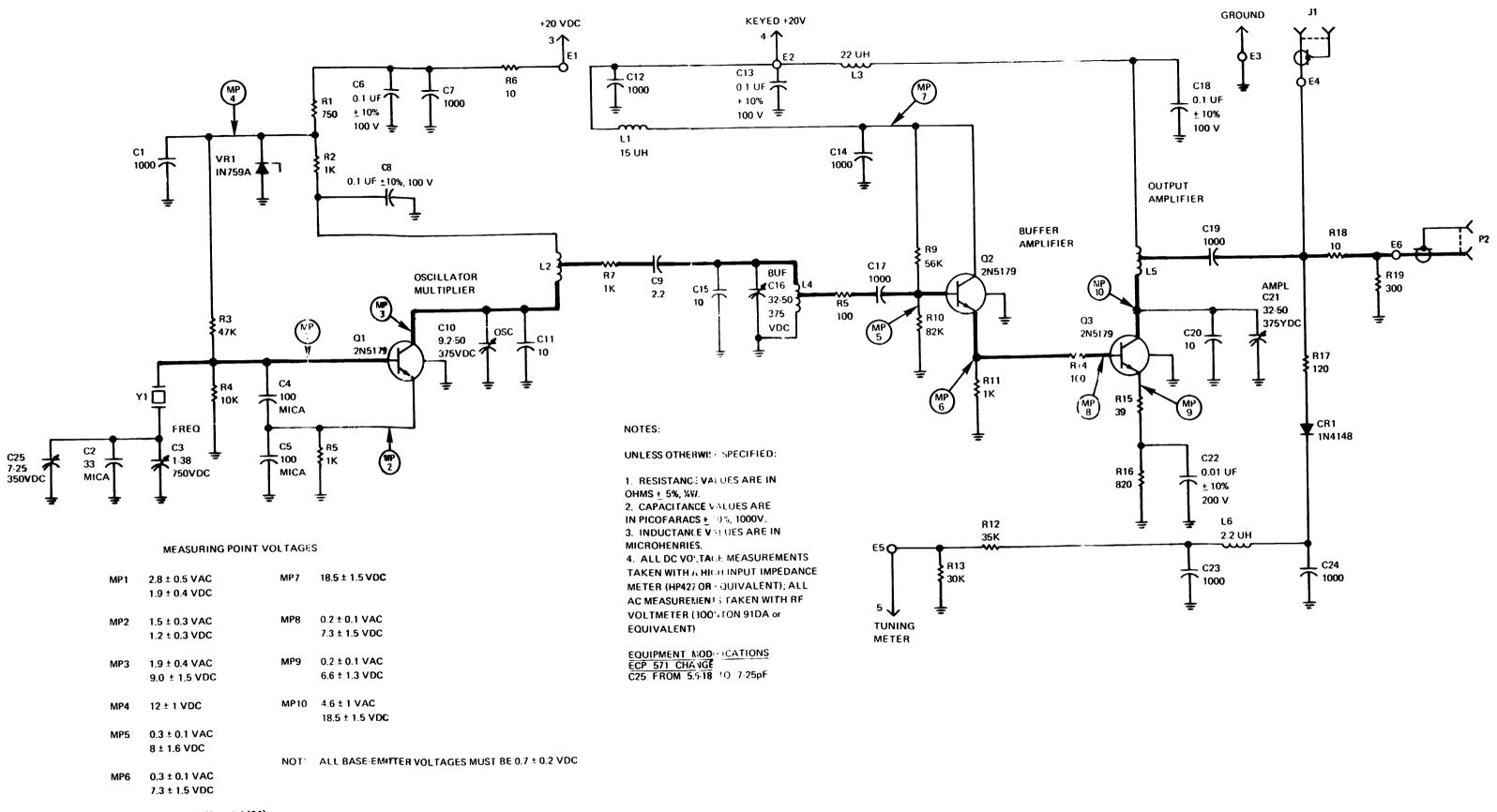

Figure 11-15. Oscillator-Multiplier A1(M)

#### AF P 6500.1 CHG 361 Chap 356 1/28/83 OSCILLATOR-MULTIPLIER A1(M)

The oscillator-multiplier module is directly interchangeable with the oscillator-synthesizer module. The oscillator-multiplier module utilizes a fundamental crystal. Frequency accuracy is determined by "pulling" the crystal. Tuning to the exact frequency is accomplished by monitoring the frequency with a counter or frequency meter connected to J1.

The oscillator-multiplier module consists of a crystal-controlled oscillator and multiplier stage, a buffer amplifier stage, and an output amplifier stage. The oscillator-multiplier requires a fundamental mode crystal operating in the frequency range of 11.25 MHz to 99.975 MHz. The output frequency from the module is 5 times the crystal frequency.

Oscillator stage Q1 is a modified Colpitts circuit. Crystal Y1 operates in an antiresonant mode. Paralleled capacitor combination, C2, C3, and C25, in series with the crystal, controls the frequency. Capacitor C25 is internally adjusted at the factory so that the desired oscillator frequency falls at the C3 adjustment range midpoint. Capacitors C4 and C5 form the feedback divider characteristic of the Colpitts configuration. Transistor Q1 is biased into conduction by voltage divider R3 and R4. The Q1 emitter return is R5. The Q1 collector circuit is tuned to the oscillator fifth harmonic by the resonant circuit L2-C10, C11. Capacitor C10 is the front panel tuning element. The Q1 d.c. input is regulated at 12 volts by VR1. Oscillator power supply isolation is by R1, R6, C6, and C7. The tuned circuit RF ground is through C8. Collector circuit current limiting is provided by R2. Resistance R7 is impedance isolation between the oscillator-multiplier tuned circuit and buffer bandpass filter L4-C15, C16, tuned to the crystal fifth harmonic.

Buffer amplifier Q2 is an emitter follower that minimizes shunt loading on the L4-C15, C16 filter preceding it, and drives the output amplifier stage following it. Capacitor C16 is the front panel tuning element. Voltage divider R9, R10 provides base bias for Q2. Resistor R11 is the emitter load.

Stage Q3 is the output RF amplifier of the oscillator-multiplier module. The signal is applied to the Q3 base by direct coupling from the buffer amplifier via parasitic suppression resistor R14. Resistors R15 and R16 provide emitter bias. The collector circuit is tuned by L3-C20, C21 to the crystal fifth harmonic. Capacitor C21 is the front panel tuning element: The output passes through attenuator network R18, R19, which buffers the output to the driven stage, and stabilizes the output impedance to approximately 50 ohms.

The signal is branched from the output stage via R17 into diode detector CR1 for metering the signal level for tuning purposes. RF filtering is provided by network L6, C23, and C24. Resistors R12 and R13 determine the scale factor of the external indicating meter.

An external signal generator can be used if desired. To do so, crystal Y1 is removed, disabling the oscillator, and 1-2 V rms is applied to J1 from the external signal generator. The signal generator must be set to the desired output frequency, i.e., 5 times the crystal frequency. Front panel tuning capacitors C16 and C21 are then adjusted for maximum output on the meter.

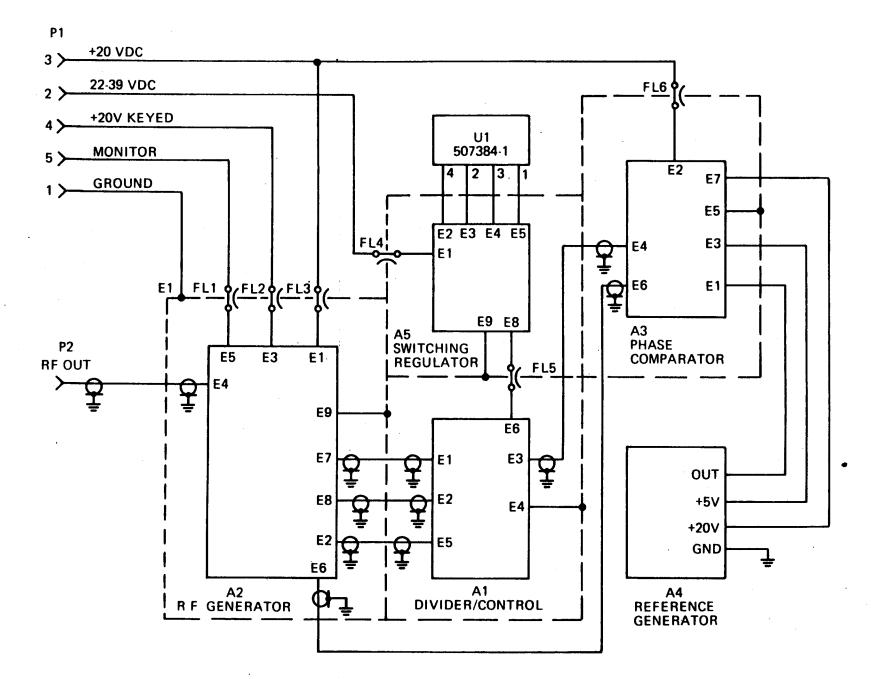

#### **OSCILLATOR – SYNTHESIZER A1(S)**

The oscillator-synthesizer generates selectable stable frequencies by a voltage-tuned oscillator. The selected oscillator output frequency is fed to a prescaler counter which divides the frequency by 4 and feeds it to a variable counter. The variable counter further divides the frequency by a ratio of 9,000 to 15,999 as determined by the settings of the frequency select thumbwheels. The division ratio of the counter is such that when the voltage-tuned oscillator is generating the correct frequency, the output of the variable counter is 1.5625 kHz. This output signal is fed to a phase detector and compared with a 1.5625 kHz reference signal. The 1.5625 kHz reference signal is derived from a precision crystal-controlled oscillator and a digital fixed-frequency divider counter. The phase difference between these two signals determines the d.c. voltage which controls the voltage-tuned oscillator is + 14 dBm  $\pm 3$  dBm.

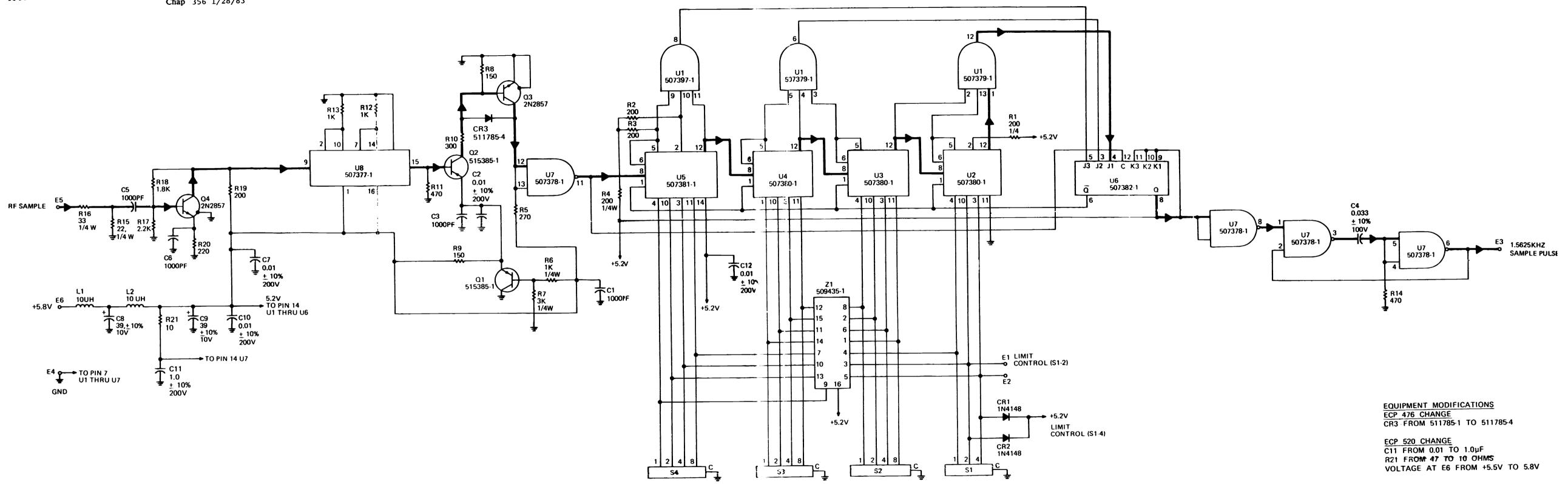

Figure 11-17. Divider/Control A1A1(S)

11-28/11-27 (blank)

GTLS: UNLESS OTHERWISE SPECIFIED: 1. ALL RESISTANCE VALUES ARE IN OHMS, ±5%, 1/8 W 2. ALL CAPACITANCE VALUES ARE IN MICROFARADS, ±20%, 1000V

#### DIVIDER/CONTROL A1A1(S)

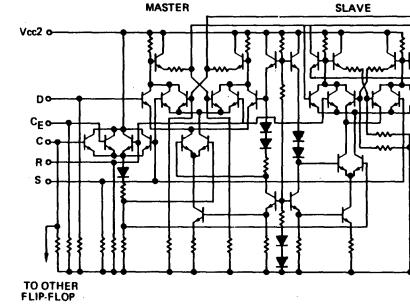

This board determines the output frequency. The board contains a prescaler (divide by 4) and a variable counter with its associated frequency selection switches. The RF sample from the RF generator board is fed through attenuator R15 and R16. C5 is a d.c. block which couples the RF to the base of amplifier Q4. This device places the RF at a d.c. level of about 3.2 volts (by virtue of bias resistors R17 and R18) which is the optimum input level for U8. U8 is an emitter-coupled logic dual-D flip-flop which is hooked up to divide the input RF signal (56.25 MHz to 99.9937 MHz) by 4. The output of U8 is fed to an emitter-coupled pair Q1 and Q2. This circuit amplifies the output of U8 and shifts the signal level to that of TTL (transistor-transistor logic). Q3 is used as a saturating switch which drives the first logic gate.

The variable counter number (divide by N) is essentially a chain of programmable counters constructed entirely with monolithic integrated circuits. The division ratio N ranges from 9,000 to 15,997 and is programmed by generating binary logic levels with the four-digit frequency selector thumbwheel switches. The first three switches are inverted "nines" complement binary coded decimal (bcd). Switch S4 is hexadecimal code which programs U5 (divide by 16). S1, S2, and S3 program U2, U3, and U4 respectively, which are divide by 10 counters. Assuming the thumbwheels are set to 99.9937, this means all switches are made placing a "low" on all the inputs, so the division ratio is 15,997. Thus the signal is coupled through the NAND gate (U7) following Q3 and into U5. This divides the input 24.9984375 MHz pulse train by 16. The output of U5 drives the input of U4 which divides by 10. This signal then drives U3, which drives U2, each of which divide by 10. When the counter reaches 99.9937 (by dial), or 15,997 pulses have been counted, the inputs to the U1 AND gates are all high, which drive a three-input AND gate in U6, causing it to change states. This resets U2, U3, U4, and U5, and causes a pulse out of pin 8 of U6 into a NAND gate of U7. This drives another NAND gate, whose output is shaped by C4 and R14 to drive another NAND gate, which is the output of the divider. These NAND gates are used to shape the output of U3 to a narrow pulse (approximately 10  $\mu$ s) which drives the phase comparator.

If the thumbwheels are set to numbers other than 99.9937, the inputs to the divider counters are made high through the switch. Z1 is a resistor network consisting of 15 each 4.7-kilohm pull-up resistors with one lead common to pin 16 (B+). No change will occur until the data strobe drops to a logic zero (Q of U6 upon full count). At that time the data on the inputs will be transferred to their associated counters and the count will take up from there on the next clock pulse. Under these conditions, the count required will be shortened by the amount of the preset inputs.

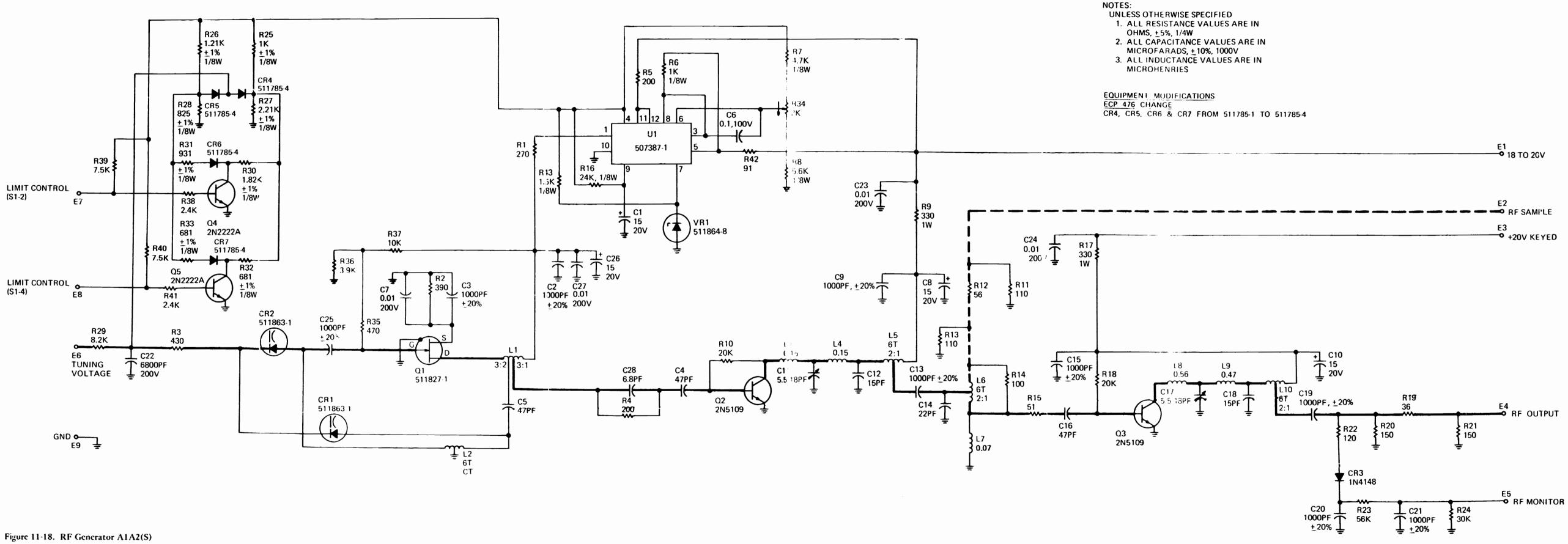

#### **RF GENERATOR A1A2(S)**

The RF generator provides the output signal of the synthesizer, as well as driving the divider control prescaler. The printed wiring board contains the oscillator, limit controls for the oscillator, a buffer amplifier, a final amplifier, and a voltage regulator. The oscillator is basically a voltage-tuned Hartley circuit, with tank L2, CR1, and CR2. CR1 and CR2 are voltage variable capacitors (varactor diodes) whose capacity is dependent on the amount of reverse voltage. This control voltage is obtained from the output of the phase comparator, and is coupled through R29 and R3, with C22 used as a bypass. Q1 is a high-frequency field-effect transistor, with R1, R2, R35. R36, and R37 providing bias and feedback. C2, C3, C7, C26, and C27 are all bypass capacitors, and C5 and C25 are blocking capacitors. L1 is an autotransformer and is used to couple the signal out to the buffer amplifier Q2, through R4, C4, and C28.

R10 is a d.c. feedback resistor, and R9 is the collector load. L3, C11, L4, and C12 are low-pass filter sections to reduce the second harmonic, with C8, C9, and C23 used as bypasses. L5 is an autotransformer and couples the signal into signal splitter L6. R11, R12, and R13 are used to attenuate the signal which goes back to the divider control. L7, C16, and R15 match the input impedance of Q3, the final amplifier. R18 is the d.c. feedback with R17 the collector load. L8, C17, L9, and C18 are two low-pass filter sections to reduce harmonics, with C10, C15, and C24 bypasses. L10 is an autotransformer which couples the signal to C19, a d.c. block. R19, R20, and R21 are used to attenuate the signal to provide isolation from loading effects of the synthesizer output. R22, CR3, C20, R23, C21, and R24 form an RF detector which indicates the presence of RF on the receiver front panel L0 test point.

U1 is a transistor array of two individual transistors and two transistors internally connected as a Darlington circuit. U1 is used as a voltage regulator, with VR1 the zener reference. Q4 and Q5 are used to limit the control line voltage to the oscillator. They are tuned on by S1 on the divider control. This switch has binary coded decimal outputs, and depends on the frequency selected by the first thumb-wheel switch. Either or both Q4 and Q5 may be turned on. When either is turned on, a voltage limit is developed across the precision resistors which are coupled to the control line. This voltage overrides the control voltage from the phase comparator and limits the oscillator range. This prevents the synthesizer from locking falsely on a harmonic.

#### PHASE COMPARATOR A1A3(S)

The phase comparator converts the difference between the phase of the variable counter and the reference generator to an error voltage. Note that the frequency of these two signals is the same, but they differ in phase. Q3 is a voltage regulator of the capacitor multiplier type. C9 and R13 are filters for the regulated 18 to 20 V d.c. input supply. VR1 is the zener diode which provides the reference voltage. C7 and C8 are bypass capacitors for VR1, with R11 and R12 the bias for Q3. C5, C6, and R9 are filters for the regulated output of Q3. R28 is a decoupling component to further filter the input voltage to the reference generator. R27 and VR2 establish the regulated +5V for the reference generator. Q1 is a switch for the square wave from the reference generator. R1, R2, and C1 differentiate the leading edge of the incoming square wave to cause a quick turn-on of Q1. This drives the ramp generator Q2. When Q1 conducts, it discharges C2 and C3, and pulls the base and emitter of Q2 toward ground. After Q1 turns off, C2, C3, R4, and R5 are used as an RC time constant to create a ramp. Since Q2 is an emitter follower, the output is bootstrapped back to the base to increase the ramp. R7 is used to linearize the ramp. R6 and R8 are bias resistors for Q2.

Q5 is a switch for the negative pulse from the divider control circuit which is differentiated by C10 and R15. R14 and R16 are bias resistors. C11 and R17 couple the leading edge of the signal to the gate of Q6 while also providing a high impedance. The ramp generator output is applied to the source of Q6 and is a varying d.c. voltage. When the sample pulse from the divider control is applied, Q6 conducts the d.c. level that is on the source at that particular instant, and this d.c. level is stored on C12. This level is held until the next sample pulse. Thus the circuit "samples" the d.c. level of the ramp, and "holds" it. This "hold" voltage is a continuous voltage that is proportional to the phase difference of the two input signals. During search mode (before phase lock occurs), CR1 or CR2 conduct because there is greater than 0.6 volt across them. After phase lock occurs, the voltage differential is low and **R25** provides isolation for any noise that might be present. U1 is a high input impedance operational amplifier which is used as a d.c. level shifter to provide the proper d.c. level for the voltage-tuned oscillator. It has almost unity gain, with R19 and R26 providing the nominal operating level. R21, C14, R22, C15, R23, C16, R24, and C18 form a multisection low-pass filter which is used to remove any undesired a.c. signal from the control voltage to the voltage-tuned oscillator. During search mode, most of the filter is bypassed by L1 and CR2 or CR3, which conduct when the voltage differential is greater than 0.6 volt.

#### EQUIPMENT MODIFICATIONS

| ECP | 520 | CHAN | GES |

|-----|-----|------|-----|

|     |     |      |     |

CHANGE R2 FROM 1M TO 1.3M CHANGE E8 VOLTAGE +5.5 Vdc TO 5.8 Vdc ECP 648 CHANGE CHANGE U1 TO BE EITHER &PIN (507386-2) or 14-PIN (507386-1) AUD NOTE 3

ECP 470 CHANGES DELETE VR1 (1N754A) DELETE R7 (20 OHMS) DELETE R8 (1K) DELETE CR1 (2N2323)

#### SWITCHING REGULATOR A1A5(S)

This printed wiring board consists of an input filter, a power switch driver, an overvoltage shutdown circuit, and an output filter. The input filter consists of C1, C2, and L3. U1 is the switch driver, with R3 used as a short circuit protector. R4, R5, and R6 form a voltage divider string. L1 is an inductor which filters the d.c. pulses from the power switch. Operation consists of U1 being turned on by the feedback sensor after it drops to a sufficiently low value. It is an operational amplifier with its own internal reference diode. It operates as a switch and is either on or off. It drives an integrated circuit mounted on the back of the synthesizer which is a power switch. This switch conducts the unregulated d.c. for short pulses, operating at 40 kHz switching frequency.

Figure 11-20A. T0-5/T0-99 Installation in 14-Pin Dual Inline Package (DIP) Socket

Voltage regulator U1 in the synthesizer switching regulator (A1A5) is no longer manufactured in the 14-pin dual inline package. U1 may be replaced with either the 14-pin DIP or with the 8-pin T0-5 or T0-99 package that is electrically equivalent. Use one or the other; do not install both on the sme circuit card. Figure 11-20A illustrates how the 8-pin T0-5 or T0-99 is to be installed to replace the 14-pin DIP in case of failure of the 14-pin DIP.

11-39/11-40 (blank)

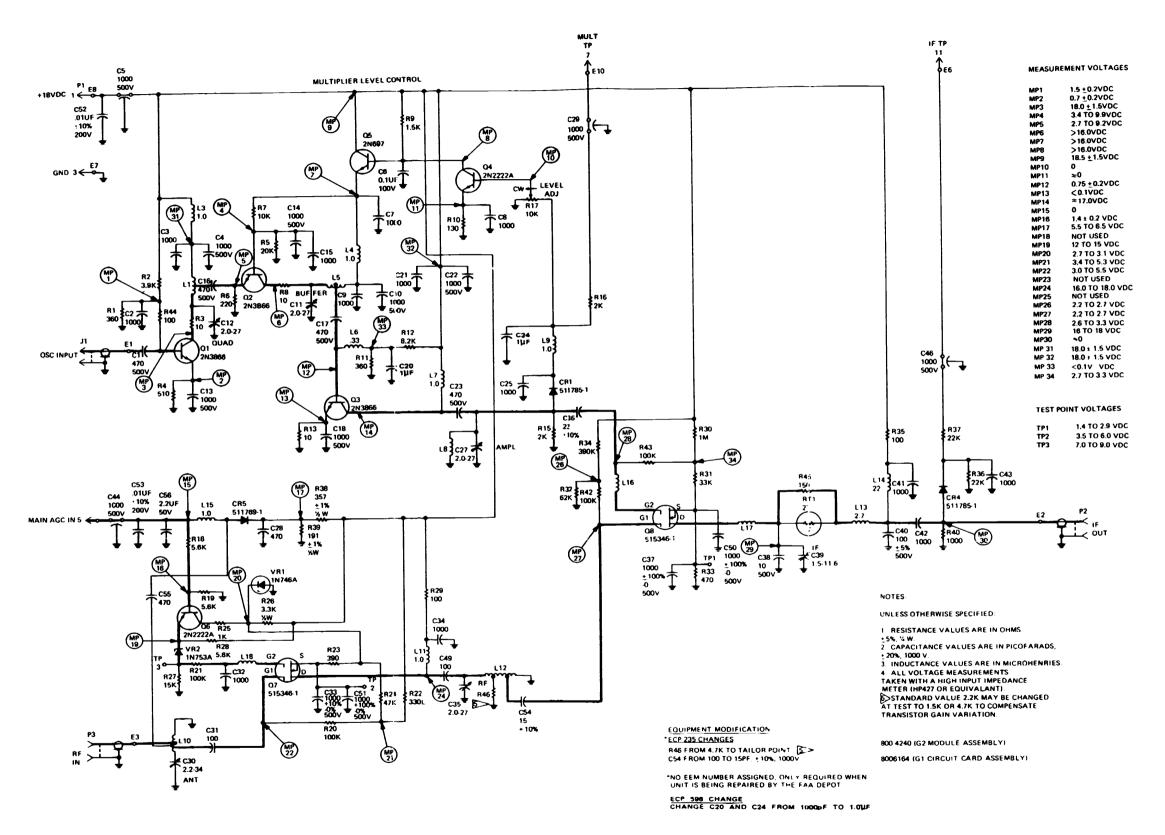

## Figure 11-21. Mixer/Multiplier (UHF) A2 G1

#### **MIXER/MULTIPLIER (UHF) A2 G1**

The uhf mixer/multiplier module consists of an agc-controlled RF stage, a mixer stage, a local oscillator frequency quadrupler stage, a buffer amplifier stage, an amplifier stage, a feedback amplifier stage and a series regulating stage for gain control. The RF input from the antenna is directly coupled to a tap on L10. The input tuned circuit consists of L10 and variable capacitor C30 which is peaked at the incoming RF. The input RF signal is coupled through C31 to gate 1 of the dual gate field effect transistor RF stage Q7. The source of Q7 is supplied through R23 and R24 from the cathode of zener diode VR1.

The voltage at gate 2 of Q7 is developed by the voltage divider consisting of R28, VR2, and R27 and is supplied to gate 2 of Q7 through R21 and L18. The agc input is connected through R18 to common emitter agc amplifier Q6. The agc input is also connected through L15 and pin diode CR5 to voltage divider R38 and R39. As the agc voltage level increases with increasing RF signal level, the pin diode is driven into conduction and thus attenuates incoming signals and prevents Q7 and Q8 from being overdriven. As the agc voltage increases, Q6 is driven harder into conduction and reduces the voltage supplied to gate 2 of Q7 by shunting VR2 and R27 in the voltage divider that provides bias for gate 2 of Q7.

The output at the drain of Q7 is coupled through C49 to parallel tuned circuit L12 and C35. C35 is adjustable to peak the signal at the received RF. The signal is then coupled through C54 to gate 1 of the dual-gate field effect transistor mixer stage Q8. The quadrupled crystal oscillator frequency is applied to gate 2 of Q8 and the intermediate frequency of 20.6 MHz is produced at the drain of Q8. Variable capacitor C39 is adjusted for maximum IF signal output. Impedance matching for the output circuit of Q8 is provided by matching network C38, C39, L13, and C40. Temperature compensation is provided by R45 and thermistor RT1. The IF signal is also detected by CR4 and applied through R37 to the receiver front panel major test point MIXER OUT as a positive voltage level.

The output from the oscillator module is coupled through C1 to the base of quadrupler Q1. Bias for Q1 is supplied through R44 from the voltage divider R1 and R2. C12 is adjusted to peak the signal in the collector of Q1 at four times the frequency applied to the base. The quadrupled frequency is coupled through C16 to the emitter of common base buffer amplifier Q2. C11 is adjusted to peak the signal at the collector of Q2 at four times the oscillator frequency. The signal is coupled through C17 to the base of amplifier Q3. C27 is adjusted to peak the signal at the collector of Q3 at four times the oscillator frequency. The signal is coupled through C16 to gate 2 of Q8. The voltage at the collector of Q3 is also detected by CR1 and applied through potentiometer R17 to the base of feedback amplifier Q4. The collector voltage of Q4 in turn controls the base to emitter bias for series regulator Q5. Q2 operates between cutoff and saturation. Q5 controls the output of Q2 by controlling the d.c. supply voltage to Q2 and thus the operating point of Q2. The detected voltage from CR1 is also applied to the front panel major test point MULT.

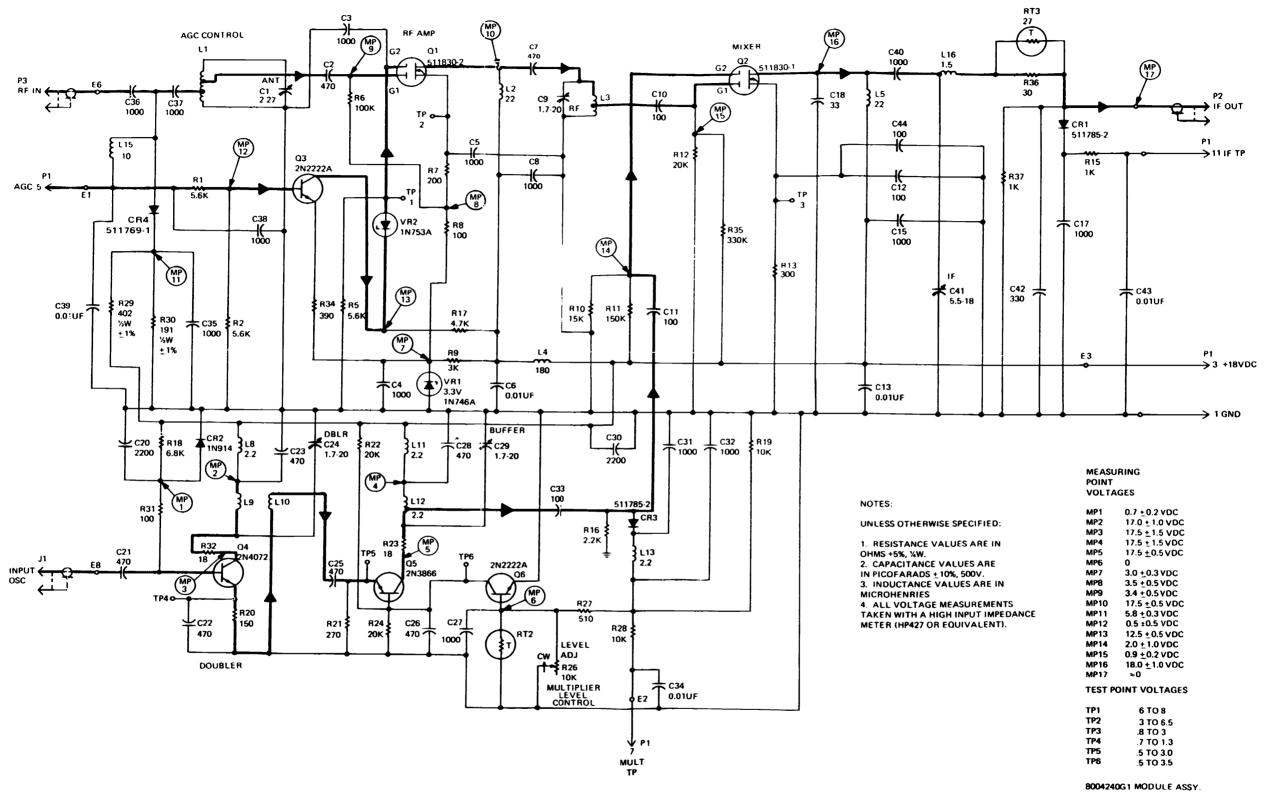

## Figure 11-22. Mixcr/Multiplier (UHF) A2 G2

#### MIXER/MULTIPLIER (UHF) A2 G2

The uhf mixer/multiplier module consists of an agc-controlled RF stage, a mixer stage, a local oscillator frequency quadrupler stage, a buffer amplifier stage, an amplifier stage, a feedback amplifier stage, and a series regulating stage for gain control. The RF input from the antenna is directly coupled to a tap on L10. The input tuned circuit consists of L10 and variable capacitor C30 which is peaked at the incoming RF. The input RF signal is coupled through C31 to gate 1 of the dual gate field effect transistor RF stage Q7. The source of Q7 is supplied through R23 from the cathode of zener diode VR1.

The voltage at gate 2 of Q7 is developed by the voltage divider consisting of R28, VR2, and R27 and is supplied to gate 2 of Q7 through R21 and L18. The agc input is divided by R18 and R19 and applied to the base of common emitter amplifier stage Q6. The agc input is also connected through L15 and pin diode CR5 to voltage divider R38 and R39. As the agc voltage level increases with increasing RF signal level, the pin diode is driven into conduction and thus attenuates incoming signals and prevents Q7 and Q8 from being overdriven. As the agc voltage increases, Q6 is driven harder into conduction and reduces the voltage supplied to gate 2 of Q7 by shunting VR2 and R27 in the voltage divider that provides bias for gate 2 of Q7.

The output at the drain of Q7 is coupled through C49 to parallel tuned circuit L12 and C35. C35 is adjustable to peak the signal at the received RF. The signal is then coupled through C54 to gate 1 of the dual-gate field effect transistor mixer stage Q8. The quadrupled crystal oscillator frequency is applied to gate 2 of Q8 and the intermediate frequency of 20.6 MHz is produced at the drain of Q8. Variable capacitor C39 is adjusted for maximum IF signal output. Impedance matching for the output circuit of Q8 is provided by matching network C38, C39, L13, and C40. Temperature compensation is provided by R45 and thermistor RT1. The IF signal is also detected by CR4 and applied through R37 to the receiver front panel major test point MIXER OUT as a positive voltage level.

The output from the oscillator module is coupled through C1 to the base of quadrupler Q1. Bias for Q1 is supplied through R44 from the voltage divider R1 and R2. C12 is adjusted to peak the signal in the collector of Q1 at four times the frequency applied to the base. The quadrupled frequency is coupled through C16 to the emitter of common base buffer amplifier Q2. C11 is adjusted to peak the signal at the collector of Q2 at four times the oscillator frequency. The signal is coupled through C17 to the base of amplifier Q3. C27 is adjusted to peak the signal at the collector of Q3 at four times the oscillator frequency. The signal is coupled through C16 to gate 2 of Q8. The voltage at the collector of Q3 is also detected by CR1 and applied through L9 and potentiometer R17 to the base of feedback amplifier Q4. The collector voltage of Q4 in turn controls the base to emitter bias for series regulator Q5. Q2 operates between cutoff and saturation. Q5 controls the output of Q2 by controlling the d.c. supply voltage to Q2 and thus the operating point of Q2. The detected voltage from CR1 is also applied to the front panel major test point MULT.

11-47/11-48 (blank)

8004351G1 CIRCUIT CARD ASSY.

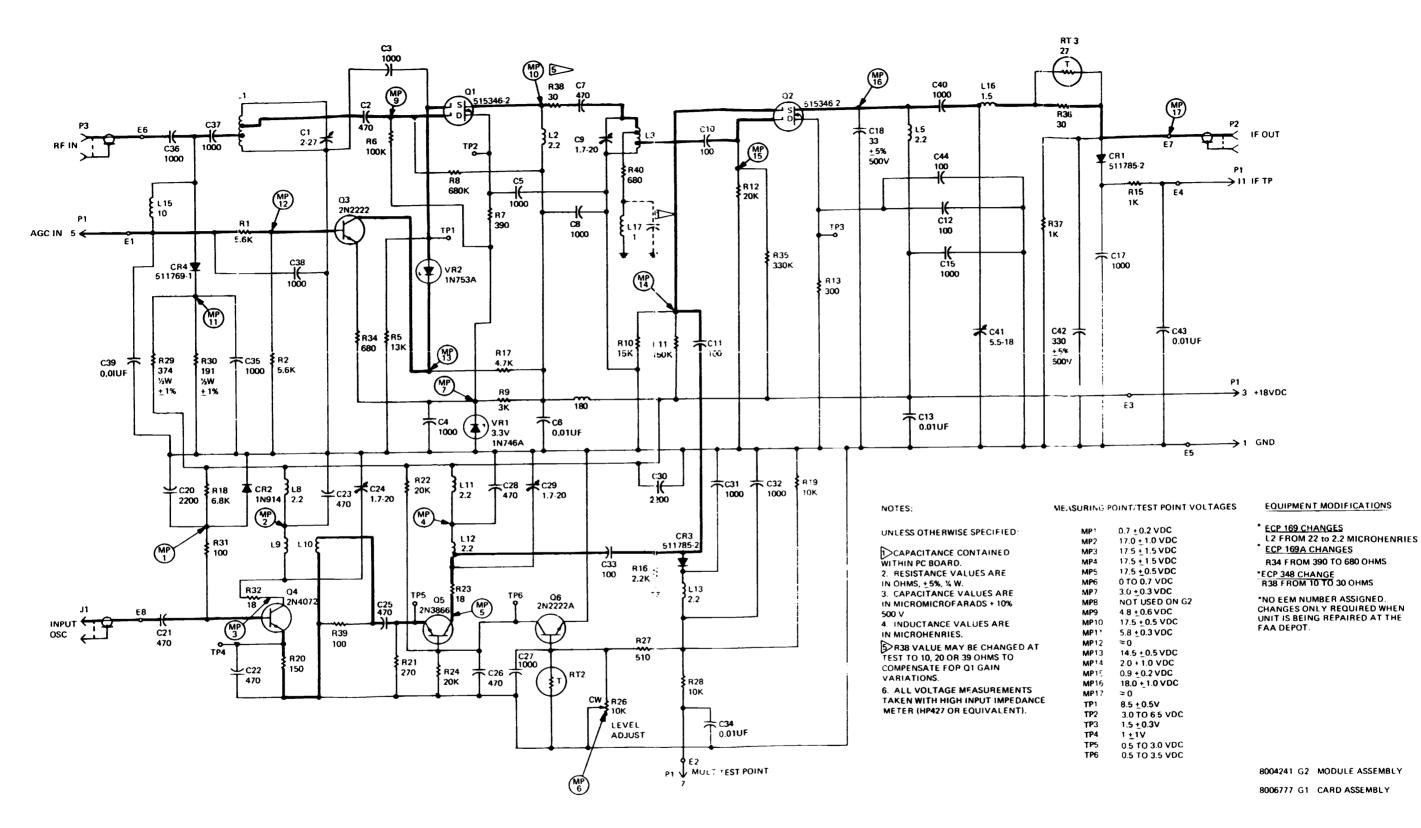

Figure 11-23. Mixer/Multiplier (VHF) A2 G1

#### MIXER/MULTIPLIER (VHF) A2 G1

The vhf mixer/multiplier module consists of a temperature-compensated and agc-controlled RF stage, a mixer stage, a local oscillator frequency doubler stage, and a buffer amplifier with a temperature compensated feedback stage. Optimum gain for the module is 12 to 14 dB. The RF input from the antenna is coupled through C36 and C37 to a tap on L1. Resonance at the received frequency is achieved by adjusting variable capacitor C1. The signal from a tap on L1 is coupled through C2 to gate 1 of dual-gate field effect transistor Q1. The source of Q1 is supplied through R7 and R8 from the cathode of zener diode VR1. The +3.3 volts established by the diode, is used to raise the source of Q1 sufficiently above ground so that the gates may be negatively biased relative to the source.

This voltage at gate 2 of Q1 is developed from the agc input to the module. The agc input is divided by R1 and R2 and applied to the base of common-emitter amplifier stage Q3. The agc input is also connected through L15 and pin diode CR4 to the voltage divider R29 and R30. As the agc voltage level increases with increasing RF signal level, the pin diode is driven into conduction and thus attenuates incoming signals and prevents Q1 and Q2 from being overdriven. The collector of Q3 becomes less positive as the input agc level becomes more positive. This voltage is a bias voltage direct coupled to gate 2 of Q1 after being level changed by zener diode VR2 allowing the agc input to control the level of the RF signal through Q1. The output at the drain of Q1 is coupled through C7 to parallel tuned circuit L3 and C9. C9 is adjustable to peak up the signal at the received RF frequency. The signal is then coupled through C10 to gate 1 of the dual-gate field effect transistor mixer stage Q2. The doubled crystal oscillator frequency is applied to gate 2 of Q2 and the intermediate frequency of 20.6 MHz is produced at the drain of Q2. Variable capacitor C41 is adjusted for maximum output at the IF signal. Impedance matching for the output circuit is provided by matching network L5, C18, C41, and C42. Temperature compensation is provided by thermistor RT3 and R36. The IF signal is also detected by CR1 and applied through R15 to the receiver front panel major test point MIXER OUT as a positive voltage level.

The output from the oscillator module is coupled through C21 to the base of doubler stage Q4. This signal is 0.6 to 1.0 volt rms. Approximately a +0.6 volt bias voltage is applied through R31 to the base of Q4. C24 is adjusted to peak up the signal in the collector of Q4 at twice the signal frequency impressed upon the base. This doubled frequency is induced from L9 into L10 and coupled through C25 to the emitter of buffer amplifier stage Q5. A feedback loop from Q6 establishes the voltage level on the base of Q5 thereby controlling the emitter-base bias of Q5 stabilizing its output. C29 is adjustable to resonate at the frequency produced by the preceding doubler stage. This output is coupled through C33 and C11 to gate 2 of mixer stage Q2 as previously discussed. The output is also detected by CR3 and applied through a low pass pi filter and R27 to the base of Q6. R26 provides level control by controlling the feedback voltage to Q5; temperature compensation is provided by RT2. The detected and filtered output is also applied through R28 to the receiver front panel MULT test point.

#### **MIXER/MULTIPLIER (VHF) A2 G2**

The vhf mixer/multiplier module consists of a temperature-compensated and agc-controlled RF stage, a mixer stage, a local oscillator frequency doubler stage, and a buffer amplifier with a temperature compensated feedback stage. Optimum gain for the module is 12 to 14 dB. The RF input from the antenna is coupled through C36 and C37 to a tap on L1. Resonance at the received frequency is achieved by adjusting variable capacitor C1. The signal from a tap on L1 is coupled through C2 to gate 1 of dualgate field effect transistor Q1. The source of Q1 is supplied through R7 from the cathode of zener diode VR1. The +3.3 volts established by the diode, is used to raise the source of Q1 sufficiently above ground so that the gates may be negatively biased relative to the source.

The voltage at gate 2 of Q1 is developed from the agc input to the module. The agc input is divided by R1 and R2 and applied to the base of common emitter amplifier stage Q3. The agc input is also connected through L15 and pin diode CR4 to the voltage divider R29 and R30. As the agc voltage level increases with increasing RF signal level, the pin diode is driven into conduction and thus attenuates incoming signals and prevents Q1 and Q2 from being overdriven. The collector of Q3 becomes less positive as the input age level becomes more positive. This voltage is a bias voltage direct coupled to gate 2 of Q1 after being changed in level by zener diode VR2 allowing the agc input to control the level of the RF signal through Q1. The output at the drain of Q1 is coupled through R38 and C7 to parallel tuned circuit L3 and C9. R38 is a parasitic suppression resistor. C9 is adjustable to peak up the signal at the received RF frequency. The signal is then coupled through C10 to gate 1 of the dual-gate field effect transistor mixer stage Q2. The doubled crystal oscillator frequency is applied to gate 2 of Q2 and the intermediate frequency of 20.6 MHz is produced at the drain of Q2. Variable capacitor C41 is adjusted for maximum output at the IF signal. Impedance matching for the output circuit is provided by matching network L5, C18, C41, and C42. Temperature compensation is provided by thermistor RT3 and R36. The IF signal is also detected by CR1 and applied through R15 to the receiver front panel major test point MIXER OUT as a positive voltage level.

The output from the oscillator module is coupled through C21 to the base of doubler stage Q4. This signal is 0.6 to 1.0 volt rms. Approximately a +0.6 volt bias voltage is applied through R31 to the base of Q4. C24 is adjusted to peak up the signal in the collector of Q4 at twice the signal frequency impressed upon the base. This doubled frequency is induced from L9 into L10 and coupled through C25 to the emitter of buffer amplifier stage Q5. A feedback loop from Q6 establishes the voltage level on the base of Q5 thereby controlling the emitter-base bias of Q5 stabilizing its output. C29 is adjustable to resonate at the frequency produced by the preceding doubler stage. This output is coupled through C33 and C11 to gate 2 of mixer stage Q2 as previously discussed. The output is also detected by CR3 and applied through a low pass pi filter and R27 to the base of Q6. R26 provides level control by controlling the feedback voltage to Q5; temperature compensation is provided by RT2. The detected and filtered output is also applied through R28 to the receiver front panel MULT test point.

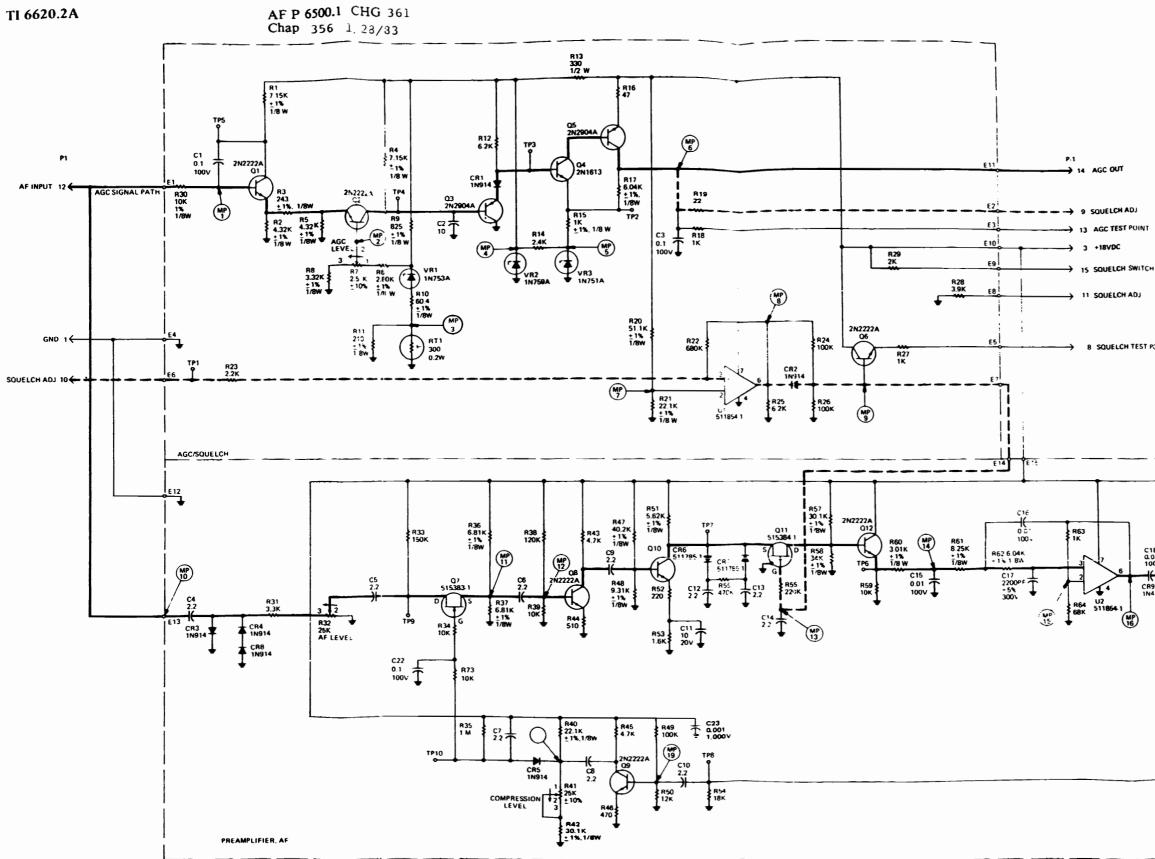

Figure 11-25. Preamplifier, AF/AGC-Squelch A3

|              | TEST POIN    | TVOLTAGES                    |                              |              |                  |

|--------------|--------------|------------------------------|------------------------------|--------------|------------------|

|              | ALL POTE     | NTIOMETERS FUI<br>SQUELCH    | LL COUNTER CLOCKW            | ISE          |                  |

|              |              | OFF                          | ON                           |              |                  |

|              | TP1          | 12.0 ± 1.0VDC                | 1.5 +0.2VDC                  |              |                  |

|              | 192          | 4.5 ±0.5VDC                  | 4.3 ±0.2VDC<br>4.5 ±0.5VDC   |              |                  |

|              | TP3<br>TP4   | 4.5 ±0.5VDC<br>3.4 ±0.5VDC   | 3.4 ±0.5VDC                  |              |                  |

|              | TP5          | 12.0 + 1.0VDC                | 12.0 ± 1.0VDC                |              |                  |

|              | TP6<br>TP7   | 9.0 ±0.5VDC<br>9.5 ±0.5VDC   | 8.9 ±0.5VDC<br>9.5 ±0.5VDC   |              |                  |

|              | TP8          | 7.5 ±0.5VDC                  | 7.5 ±0.5VDC                  |              |                  |

|              | TP9          | 9.0 ± 0.5VDC                 | 9.0 ±0.5VDC<br>9.5 ±0.5VDC   |              |                  |

|              | TP10         | 9.5 ±0.5VDC                  |                              |              |                  |

|              | MP1          | 2.5 ±0.2VDC                  | 2.5 ±0.2VDC                  |              |                  |

|              | MP2          | 4.0 + 0.5VDC                 | 4.0 ±0.5VDC                  |              |                  |

|              | MP3<br>MP4   | 0.6 ±0.2VDC<br>12.0 ±1.0VDC  | 0.6 ±0.2VDC<br>12.0 ± 1.0VDC |              |                  |

| -            | MP5          | 5.0 + 0.5VDC                 | 5.0 ±0.5VDC                  |              |                  |

| 3>           | MP6          | 3.0 ±0.5VDC<br>5.4 ±0.2VDC   | 1.8 ±0.5VDC<br>5.4 ±0.2VDC   |              |                  |

|              | MP7<br>MP8   | 17.0 ± 1.0VDC                | 0.65 ±0.05VDC                |              |                  |

| н            | MP9          | 8.5 ±0.5VDC                  | 0.32 ±0.05VDC                |              |                  |

|              | MP10<br>MP11 | 2.7 ±0.2VDC<br>9.0 ±0.5VDC   | 2.7 ±0.2VDC<br>9.0 ±0.5VDC   |              |                  |